10 spi control interface in master mode, 11 spi expander interface, 12 interrupt controller – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 169: 13 debug leds, 12 interrupt controller 9.4.13 debug leds, Table 9-4, Rtm fpga degug leds, Tsi fpga

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

169

9.4.10 SPI Control Interface in Master Mode

The RTM FPGA has a master mode SPI interface in to control peripheral devices like the MAXIM

DS26503 BITS element. The SPI interface provides a memory mapped interface to the back end

with registers for RXDATA, TXDATA, STATUS, CONTROL and SLAVESELECT.

9.4.11 SPI Expander Interface

The SPI Expander is an interface to a remote parallel I/O expansion via an additional SPI bus. The

SPI Expander continuously reads status information from and writes control information to the

remote parallel I/O expansion. The content of status and control information is accessible to

the back end Wishbone bus.

9.4.12 Interrupt Controller

The Interrupt Controller is connected to the Message Signaled Interrupt (MSI) interface of the

PCIexpress-bridge. The line based interrupts of the peripheral devices are routed to the

PCIexpress interface as MSIs. The interrupt controller provides a status register and a mask

register.

9.4.13 Debug LEDs

The RTM FPGA drives a set of eight LEDs for status notification and debug purposes. The

meaning of the LEDs is defined as follows:

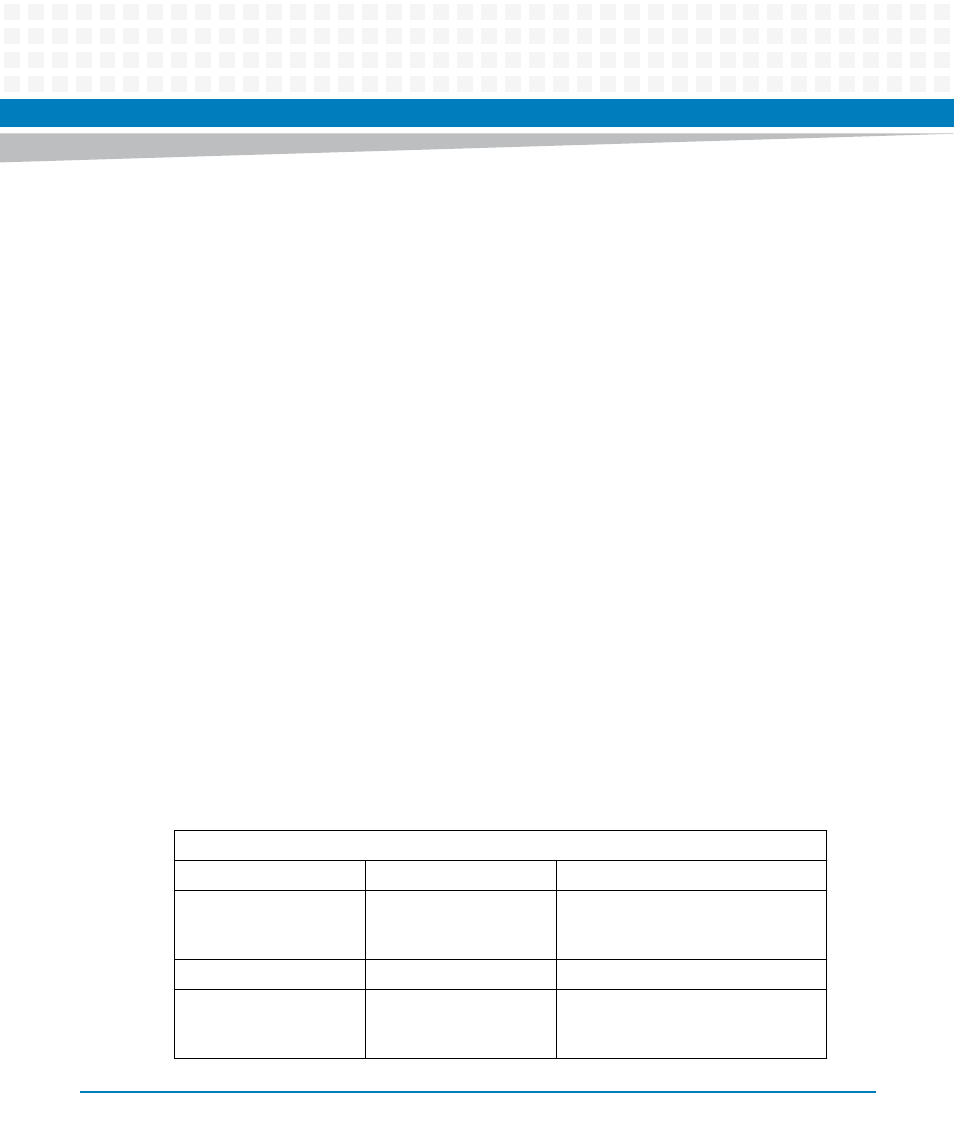

Table 9-4 RTM FPGA Degug LEDs

Power / Reset indication

DebugLed[7]

On

device loaded (reset)

On:Off 1:1

Wishbone clock 125MHz blink for

normal operation (derived from PCIe

ref clock)

DebugLed[6]

On

device loaded (reset)

On:Off 1:1

System clock 131MHz blink for

normal operation (derived from

32.768 MHz system clock)