Ext fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 332

EXT FPGA

ARTM-831X Installation and Use (6806800M76E)

332

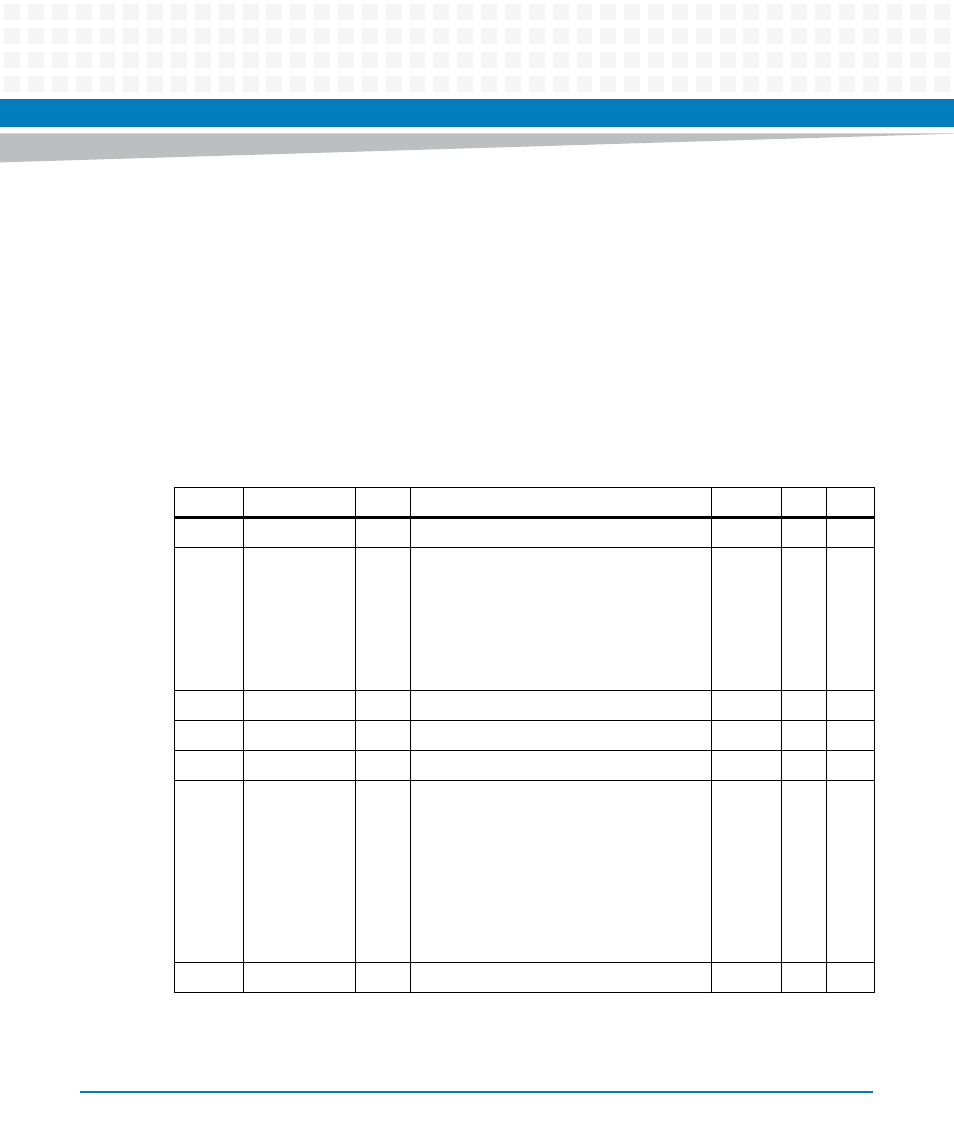

0xC0, SelRclk2

0xC4, SelRclk3

Width: 32 bit

The registers control which of 8 recovered line clocks from XRT86 framer chips 2...5 or which

of 6 recovered line clocks from upto 4 line interfaces XRT75 is switched to the respective

ExtFpgaRLClk2 or ExtFpgaRLClk3 output of the ExtFpga (SelRclk2 determines

RtmExtFpgaRLClk2, SelRclk3 determines RtmExtFpgaRLClk3. The RtmExtFpgaRLClk2 and 3

are connected to the BaseExtFpga on the front board which finally decides which RCLK to put

for synchronization to the central TDM clock generator. Depending on the module type, not all

clock sources may be present.

Bit

Acronym

Type

Description

Default

Pwr

Soft

31...26

-

-

reserved

undef

-

-

25...24

SrcBlkRLclkSe

l

RW

0b00: reserved

0b01: Xrt86BlkSel, Select clock from

Xrt86 block

0b10: Xrt75BlkSel, Select clock from

Xrt75 block

0b11: reserved

0b00

X

X

23...22

-

-

reserved

undef

-

-

21...20

-

-

reserved

undef

-

-

15...14

-

-

reserved

undef

-

-

13...12

Xrt75OutChi

pSel

RW

0b00: Xrt75OutChip0Sel, Select framer

chip 0

0b01: Xrt75OutChip1Sel, Select framer

chip 1

0b10: Xrt75OutChip2Sel, Select framer

chip 2

0b11: Xrt75OutChip3Sel, Select framer

chip 3

0b00

X

X

11

-

-

reserved

undef

-

-

- ARTM-9405 16x10GbE Installation and Use Guide (May 2014) (64 pages)

- ATCA 7370 / ATCA 7370-S Installation and Use (January 2015) (256 pages)

- ATCA 7370 / ATCA 7370-S Installation and Use (September 2014) (254 pages)

- ATCA-7350 - Integrating with Workbench User Guide (September 2014) (34 pages)

- ATCA-7350 Installation and Use (September 2014) (208 pages)

- ATCA-7365-CE Installation and Use (Jan 2015) (300 pages)

- ATCA-7365-CE Installation and Use (May 2014) (294 pages)

- ATCA-7365-CE Installation and Use (May 2014) (306 pages)

- ATCA-7368 Installation and Use (June 2014) (222 pages)

- ATCA-7475 Installation and Use (October 2014) (284 pages)

- ATCA-7480 Installation and Use (April 2015) (330 pages)

- ATCA-8330 Installation and Use (April 2015) (236 pages)

- ATCA-8320 Installation and Use (May 2014) (456 pages)

- ATCA-9305 User's Manual (May 2014) (270 pages)

- ATCA-9405 Installation and Use (October 2014) (168 pages)

- ATCA-F120 Installation and Use (August 2014) (122 pages)

- ATCA-F140 Installation and Use (September 2014) (138 pages)

- ATCA-MF106 Installation and Use (September 2014) (86 pages)

- Centellis-4440/AXP1440 Installation and Use (September 2014) (208 pages)

- Centellis 4410 (AXP-1410) Installation and Use (July 2014) (202 pages)

- Centellis 2100 Release 3.0 Installation and Use (March 2015) (192 pages)

- Centellis 2100 Release 3.0 Installation and Use (March 2015) (176 pages)

- Centellis 2000 User Card-10GE Installation and Use (May 2014) (54 pages)

- Centellis 2000 User Card-10GE with Telco Alarm Installation and Use (May 2014) (60 pages)

- COMX-CAR-210 Installation and Use (August 2014) (76 pages)

- COMX-P1022 Installation and Use (July 2014) (84 pages)

- COMX-P2020 Installation and Use (February 2015) (100 pages)

- COMX-CORE Series Installation and Use (August 2014) (128 pages)

- COMX-P2020 Installation and Use (July 2014) (100 pages)

- COMX-P4080-2G-ENP2 Installation and Use (August 2014) (70 pages)

- COMX-P4080 Installation and Use (August 2014) (126 pages)

- COMX-P40x0 ENP2 Installation and Use (August 2014) (130 pages)

- COMX-P40x0 ENP2 Installation and Use (January 2015) (140 pages)

- iVPX7225 RTM Installation and Use (April 2015) (56 pages)

- MITX-430/MITX-440-DVI-2E Installation and Use (August 2014) (118 pages)

- CPCI-6200 Installation and Use (May 2015) (234 pages)

- SCP-MITX-CORE-820-SM Installation and Use (August 2014) (132 pages)

- iVPX7225 Installation and Use (April 2015) (168 pages)

- MVME2502 Installation and Use (August 2014) (150 pages)

- MVME2502 Installation and Use (December 2014) (166 pages)

- MVME2500 VxWorks 6.8 AMP User Guide (August 2014) (40 pages)

- MVME2500 VxWorks 6.8 User Guide (April 2014) (44 pages)

- MVME3100 Single Board Computer Installation and Use (June 2014) (156 pages)

- MVME4100 Single Board Computer Installation and Use (June 2014) (136 pages)