Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 189

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

189

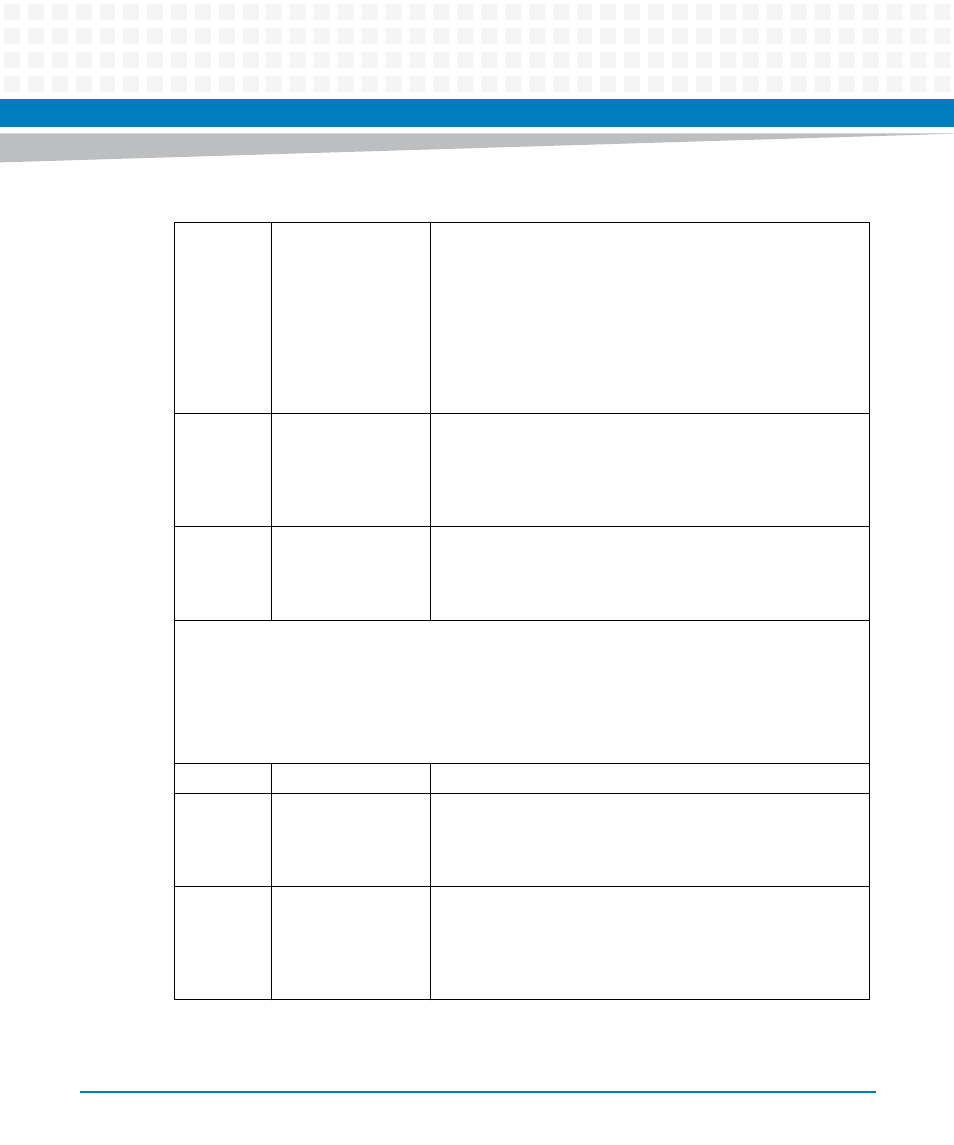

0x1614

Pmc83Xrt86LineEvt

ResReg

Pmc83 and Xrt86 Framer Line Event Status Reset Register

(32bit) [Hw: syn, WAck1, RAck1]

The bits of this register reset the respective bits in

Pmc83Xrt86LineEvtReg. Writing a 1 to a bit in

Xrt86LineEvtResReg resets the corresponding bit in

Pmc83Xrt86LineEvtReg The interrupt bit in

Pmc83Xrt86LineEvtReg is kept reset until writing a 0 to the

corresponding bit in Pmc83Xrt86LineEvtResReg re-enables its

monitor function.again.

0x1618

Pmc83Xrt86LineEvt

MaskReg

Pmc83 and Xrt86 Framer Line Event Status Mask Register

(32bit) [Hw: syn, WAck1, RAck1]

The bits of this register mask the bits of the

Pmc83Xrt86LineEvtReg. For the generation of an interrupt

(MSI) to the host via PCIE.

0x1620

StatXrt86FrmTrmRe

g

Status Xrt86 Framer Transmitter Register (8bit) [Hw: syn,

WAck1, RAck1]

The register shows the status of the Transmitter On signal to

the Xrt86 framers.

Configuration Prom Update Registers accessed through Rtm FPGA as bridge to SPI bus 0 (CfgPrmUpd)

[Hw: Cy1, InR, OutR]

Allows to update the serial configuration prom of the FPGA

Access via PCI-bus 512kByte non-pre-fetchable memory area of 64bit-bar[3,2]

indirectly bridged to SPI bus 0, where the Config Prom is connected, hereof assigned to this block:

2000...2FFF

Address

Acronym

Description

0x2000

CfgPrmUpdCtrReg

Configuration Prom Update Control Register (8bit) [Hw: syn,

WAck20, RAck20, WRP]

Controls the update of the FPGA serial configuration prom by

the host processor via SPI bus.

0x2001

CfgPrmUpdDatReg

Configuration Prom Update Data Register (8bit) [Hw: syn,

WAck100, RAck100, WRP]

Holds the write data to sent to the FPGA serial configuration

prom when written and the read data received from the FPGA

serial configuration prom when read.

Table 9-5 RTM FPGA Address map Overview (continued)