Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 275

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

275

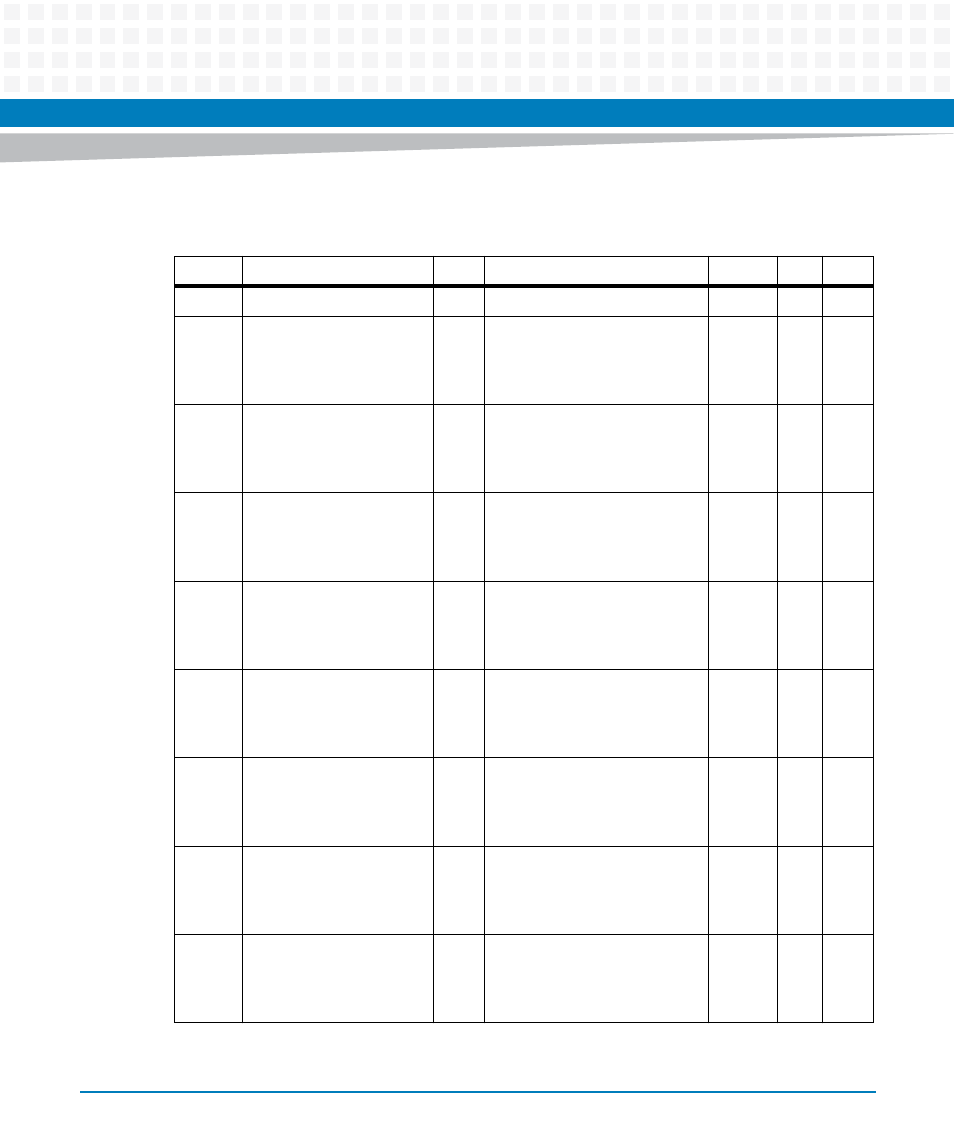

The bits of this register mask the bits of the Pmc83Xrt86LineEvtReg. For the generation of an

interrupt (MSI) to the host via PCIE.

Bit

Acronym

Type

Description

Default

Pwr

Soft

31...24

-

-

reserved

undef

-

-

23

Pmc83Chp1RcvLoSIntrpt

Mask7

RW

0b1:

Pmc83Chp1RcvLoSIntrptEnab

le7, enables chip1 receiver Line

7 loss of signal interrupt bit

0b0

X

X

22

Pmc83Chp1RcvLoSIntrpt

Mask6

RW

0b1:

Pmc83Chp1RcvLoSIntrptEnab

le6, enables chip1 receiver Line

6 loss of signal interrupt bit

0b0

X

X

21

Pmc83Chp1RcvLoSIntrpt

Mask5

RW

0b1:

Pmc83Chp1RcvLoSIntrptEnab

le5, enables chip1 receiver Line

5 loss of signal interrupt bit

0b0

X

X

20

Pmc83Chp1RcvLoSIntrpt

Mask4

RW

0b1:

Pmc83Chp1RcvLoSIntrptEnab

le4, enables chip1 receiver Line

4 loss of signal interrupt bit

0b0

X

X

19

Pmc83Chp0RcvLoSIntrpt

Mask7

RW

0b1:

Pmc83Chp0RcvLoSIntrptEnab

le7, enables chip1 receiver Line

7 loss of signal interrupt bit

0b0

X

X

18

Pmc83Chp0RcvLoSIntrpt

Mask6

RW

0b1:

Pmc83Chp0RcvLoSIntrptEnab

le6, enables chip1 receiver Line

6 loss of signal interrupt bit

0b0

X

X

17

Pmc83Chp0RcvLoSIntrpt

Mask5

RW

0b1:

Pmc83Chp0RcvLoSIntrptEnab

le5, enables chip1 receiver Line

5 loss of signal interrupt bit

0b0

X

X

16

Pmc83Chp0RcvLoSIntrpt

Mask4

RW

0b1:

Pmc83Chp0RcvLoSIntrptEnab

le4, enables chip1 receiver Line

4 loss of signal interrupt bit

0b0

X

X