Ext fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 318

EXT FPGA

ARTM-831X Installation and Use (6806800M76E)

318

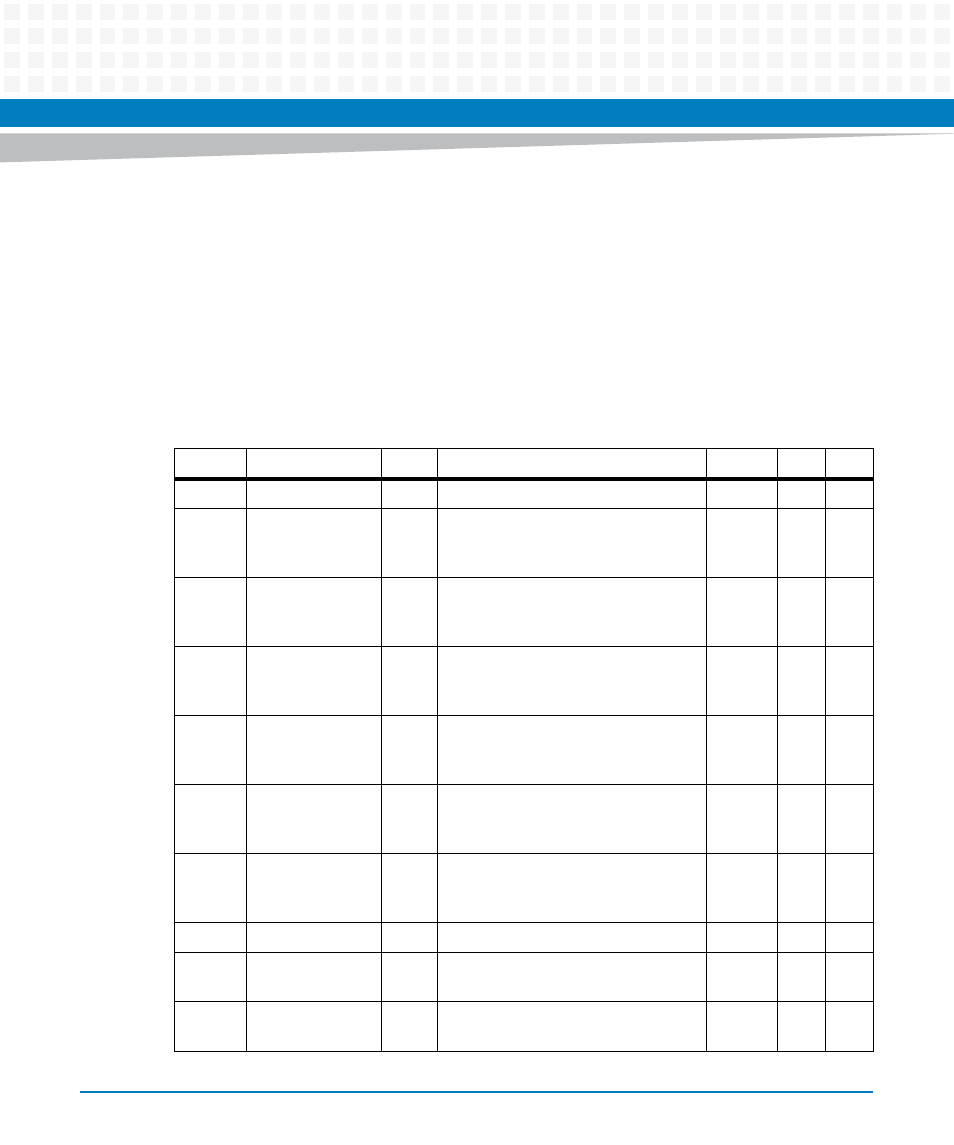

This registers monitor the loss of signal outputs of the Xrt75 framer chips 0..3 If a loss of signal

occurs, the respective bit is set. It can be reset by writing the respective bit in

Xrt75LineEvtResReg.

This registers monitor the loss of lock outputs of the Xrt75 framer chips 0..3 If a loss of lock

indicators occurs, the respective bit is set. It can be reset by writing the respective bit in

Xrt75LineEvtResReg..

This registers monitor the loss of lock outputs of the Xrt75 framer chips 0..3 If a drive monitor

output failure occurs, the respective bit is set. It can be reset by writing the respective bit in

Xrt75LineEvtResReg.

Bit

Acronym

Type

Description

Default

Pwr

Soft

31...22

-

-

reserved

undef

-

-

21

Xrt75TrmDmo5

R

0b1: Xrt75TrmDmoErr5, Transmitter

Drive Monitor of line 5 indicates

failure

0b0

F

F

20

Xrt75TrmDmo4

R

0b1: Xrt75TrmDmoErr4, Transmitter

Drive Monitor of line 4 indicates

failure

0b0

F

F

19

Xrt75TrmDmo3

R

0b1: Xrt75TrmDmoErr3, Transmitter

Drive Monitor of line 3 indicates

failure

0b0

F

F

18

Xrt75TrmDmo2

R

0b1: Xrt75TrmDmoErr2, Transmitter

Drive Monitor of line 2 indicates

failure

0b0

F

F

17

Xrt75TrmDmo1

R

0b1: Xrt75TrmDmoErr1, Transmitter

Drive Monitor of line 1 indicates

failure

0b0

F

F

16

Xrt75TrmDmo0

R

0b1: Xrt75TrmDmoErr0, Transmitter

Drive Monitor of line 0 indicates

failure

0b0

F

F

15...14

-

-

reserved

undef

-

-

13

Xrt75RcvLoL5

R

0b1: Xrt75RcvLostLock5, Receiver

Line 5 indicates loss of lock

0b0

F

F

12

Xrt75RcvLoL4

R

0b1: Xrt75RcvLostLock4, Receiver

Line 4 indicates loss of lock

0b0

F

F