Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 188

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

188

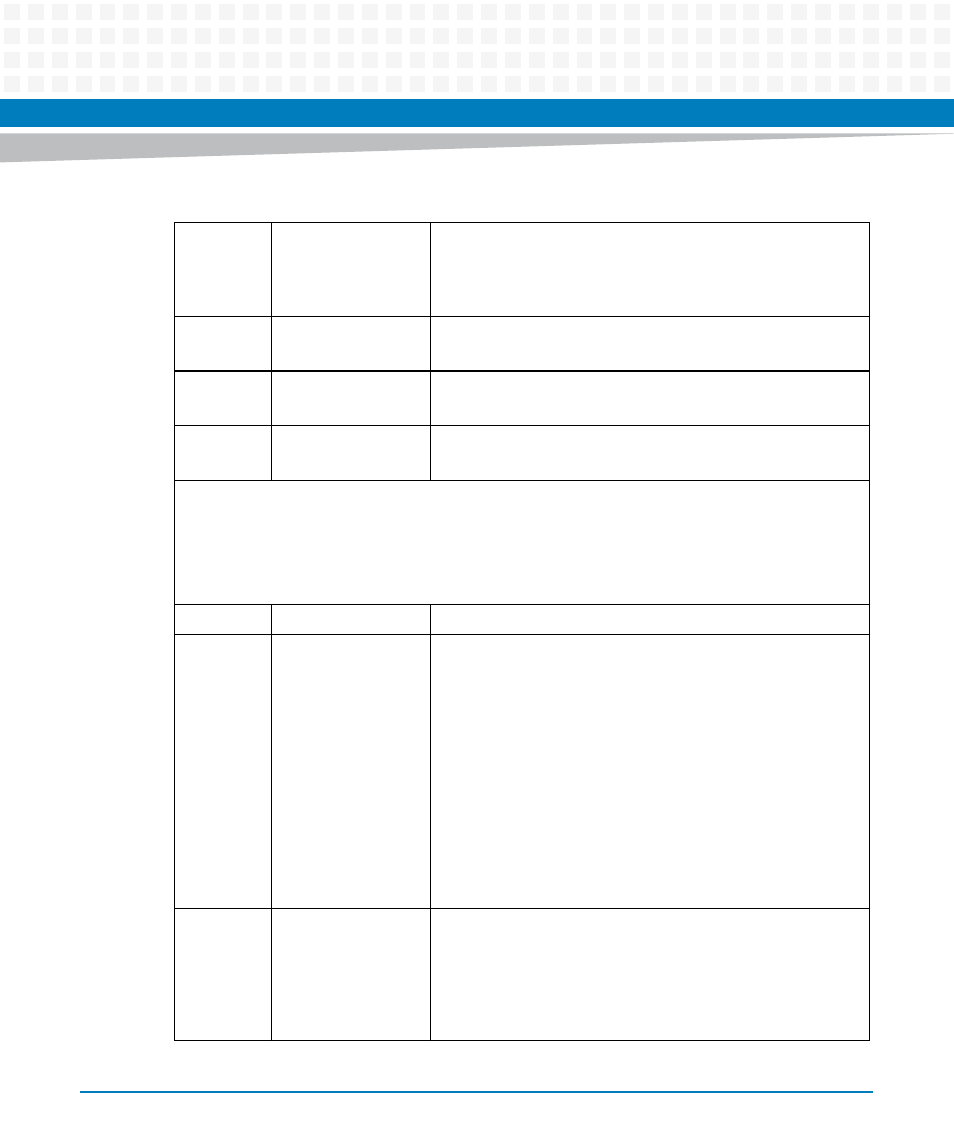

0x1504

GnrlFltInsrtReg

General Fault Insertion Register (32bit) [Hw: syn, WAck1,

RAck1]

Allows to simulate several faults initiated not by the original

source but by the host SW for test purposes

0x1508

ScratchPadReg

ScratchPad Register (32bit) [Hw: syn, WAck1, RAck1]

Registermemory without any control or status function

0x150C

TestModeCtrlReg

Test Mode Control Register (8bit) [Hw: syn, WAck1, RAck1]

Register to control testmodes

0x1510

TestReadValReg

Test Read Val Register (32bit) [Hw: syn, WAck1, RAck1]

Register to read data for Hw test purposes

Framer and Line Interface Unit Sideband Signal Registers (FrLiuSdBndRegs) [Hw: Cy1, InR, OutR]

Registers to control, control further processing or monitor signals of PMC8310-, XRT86-framers chip

0 and 1 and XRT75 Line interfaces

Access via PCI-bus 512kByte non-prefetchable memory area of 64bit-bar[3,2]

bridged to SPI bus 1, where an ExtFpga is connected, hereof assigned to this block: 1600...1FFF

Address

Acronym

Description

0x1600

0x1604

SelRclk0

SelRclk1

SelectRcvrdLclk (32bit) [Hw: syn, WAck1, RAck1]

The registers control which of 8 recovered line clocks from

XRT86 framer chips 0 and 1 or which of 8 (4 SDH, 4 E1T1)

recovered line clocks from upto 2 PMC8310 line framers is

switched to the respective RtmRLClk0 or

RtmRtmFpgaRLClk1output of the RtmFpga (SelRclk0

determines RtmRtmFpgaRLClk0, SelRclk0 determines

RtmRtmFpgaRLClk1. The RtmRtmFpgaRLClk0 and 1 are

connected to the ExtFPGA on the front board which finally

decides which RCLK 0 and 1 to put for synchronization to the

central TDM clock generator.

All clocks except the E1T1 clocks from the sonet framers are

gated with their respective LoS signal.

0x1610

Pmc83Xrt86LineEvt

Reg

Pmc83 and Xrt86 Framer Line Event Status Register (32bit)

[Hw: syn, WAck1, RAck1]

This register monitor the loss of signal outputs of the Pmc8310

framer chips 0,1and the Xrt86 framer chips 0,1. If a loss of

signal occurs, the respective bit is set. It can be reset by writing

the respective bit in Xrt86LineEvtResReg.

Table 9-5 RTM FPGA Address map Overview (continued)