Table 9-9, Pci command, Table 9-10 – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 283: Pci status, Tsi fpga

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

283

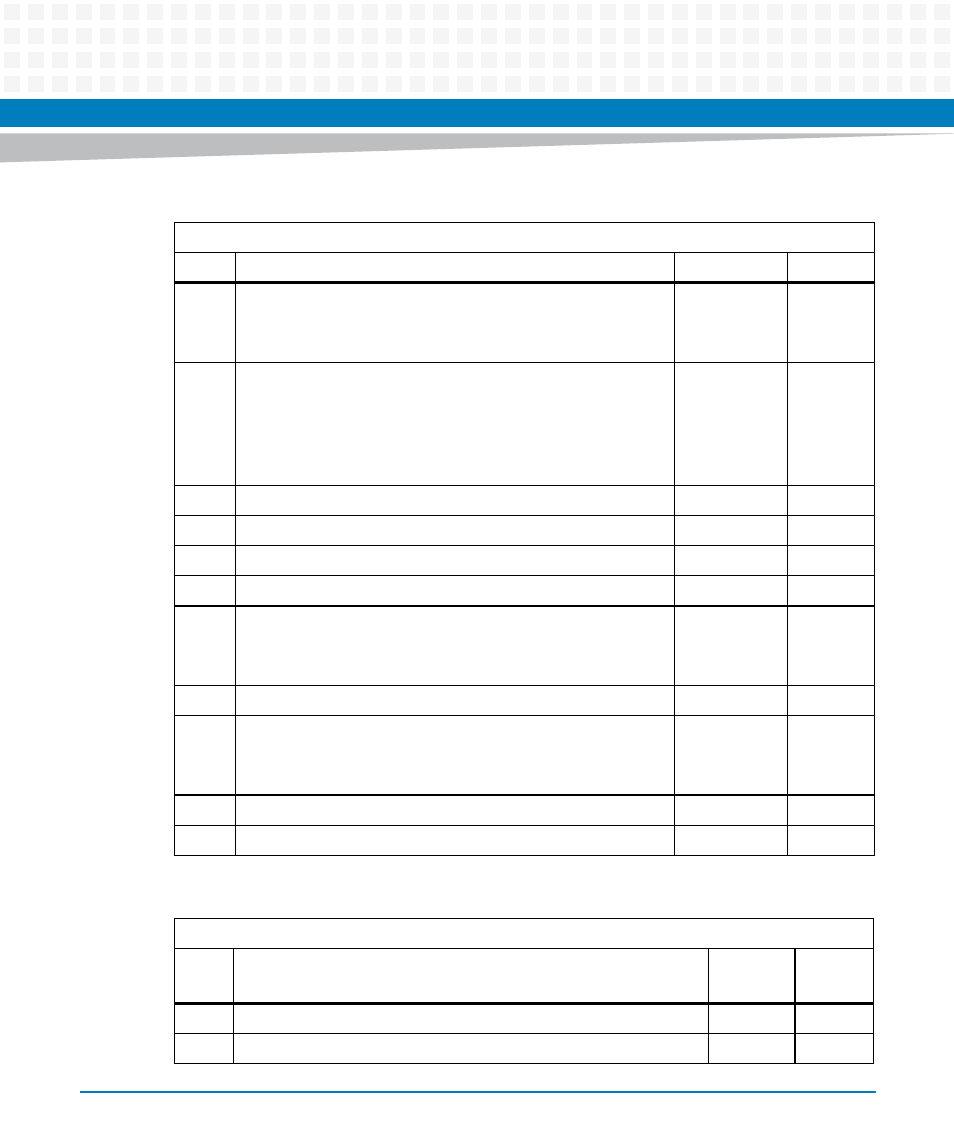

Table 9-9 PCI Command

PCI Configuration Offset: 0x04

Bit Description

Default

Access

0

IO Space

1: allows device to respond to I/O space accesses

0: disables device from responding to I/O space accesses

PCI_RST_: 0

PCI: r/w

1

Memory Space

1: allows device to respond to memory space accesses

0: prevents device from responding to memory space accesses

Default value depends on logic level of input BOT_MODE when

PCI_RST_ is deasserted. See "PCI Bus" for more information.

PCI_RST_: see

description

PCI: r/w

2

Bus Master. Not applicable for target device

0

PCI: r

3

Special Cycle. Not supported

0

PCI: r

4

Memory write/invalidate. Not applicable for target device

0

PCI: r

5

VGA palette snoop. Not supported

0

PCI: r

6

Parity Error Response

1: parity checking enabled

0: parity errors are ignored

PCI_RST_: 0

PCI: r/w

7

Wait cycle control. Device never does stepping.

0

PCI: r

8

SERR_ Enable

0: SERR_ driver disabled.

1: SERR_ driver enabled.

PCI_RST_: 0

PCI: r/w

9

Fast Back-to-Back Enable. Not applicable for target device.

0

PCI: r

15:10

Hardcoded

0

PCI: r

Table 9-10 PCI Status

PCI Configuration Offset: 0x06

Bit

Description

Default

Access

4:0

Hardcoded

0

PCI: r

5

Device is 33 MHz capable

0

PCI: r