Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 187

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

187

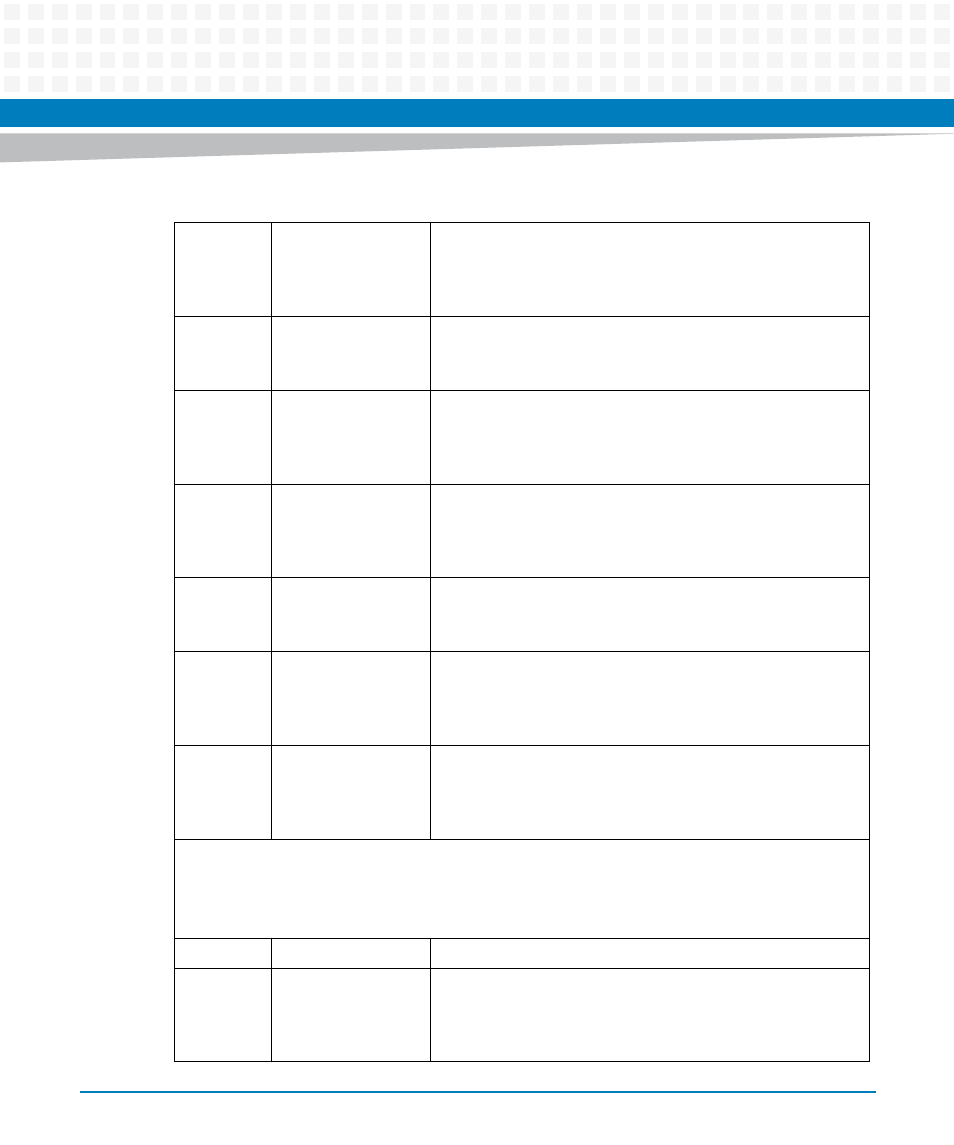

0x1494

LclBusAccessTimeou

tAddrReg

Local Bus Access Monitor Address Register (32bit) [Hw: syn,

WAck1, RAck1]

This register stores the address of the last timed out access at

the local bus

0x14A0

Spi1BusMonReg

Spi 1 Bus Access Monitor Register (8bit) [Hw: syn, WAck1,

RAck1]

This register monitors the access to the local bus

0x14A1

Spi1BusMonResetRe

g

Spi 1Bus Access Monitor Reset Register (8bit) [Hw: syn, WAck1

, RAck1]

This register resets the time out flag in the respective monitor

and address registers

0x14A4

Spi1BusAccessTime

outAddrReg

Spi 1 Bus Access Monitor Address Register (32bit) [Hw: syn,

WAck1, RAck1]

This register stores the address of the last timed out access to

the Spi 1 Bus

0x14B0

Spi2BusMonReg

Spi 2 Bus Access Monitor Register (8bit) [Hw: syn, WAck1,

RAck1]

This register monitors the access to the local bus

0x14B1

Spi2BusMonResetRe

g

Spi 2 Bus Access Monitor Reset Register (8bit) [Hw: syn, WAck1

, RAck1]

This register resets the timeout flag in the respective monitor

and address registers

0x14B4

Spi2BusAccessTime

outAddrReg

Spi 2 Bus Access Monitor Address Register (32bit) [Hw: syn,

WAck1, RAck1]

This register stores the address of the last timed out access to

the Spi 2 Bus

General Test Registers (GenTestRegs) [Hw: Cy1, InR, OutR]

General Test Registers

Access via PCI-bus 512kByte non-prefetchable memory area of 64bit-bar[3,2], hereof assigned to this

block: 1500...15FF

Address

Acronym

Description

0x1500

SoftErrFltInsrtReg

Soft Error Fault Insertion Register (32bit) [Hw: syn, WAck1,

RAck1, WTP]

Allows to simulate soft error fault initiated not by the original

source but by the host SW for test purposes.

Table 9-5 RTM FPGA Address map Overview (continued)