Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 279

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

279

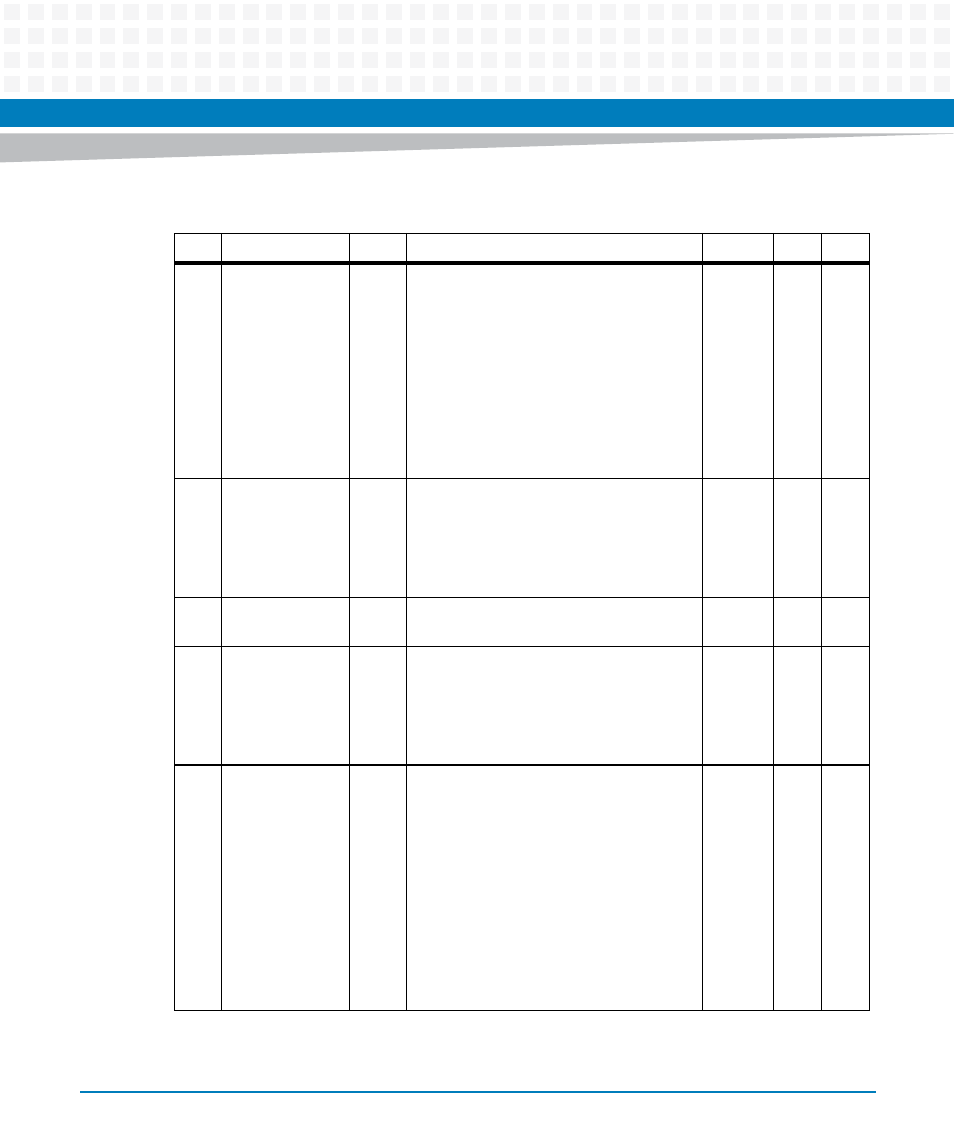

Controls the update of the FPGA serial configuration prom by the host processor via SPI bus.

Bit

Acronym

Type

Description

Default

Pwr

Soft

7

CodePrgIfEn

RW

Enable Code Program Interface

0b1: CodePrgIfEn, Program Interface

enabled. Chip Select is controlled by Bit 0

of this register and read and write

accesses to Code SPI Data Register initiate

serial transmission

0b0: CodePrgIfDis, Program Interface

disabled. Bit 0 of this register is ignored.

Write and read to Code SPI Data Register

are ignored.

0b0

X

-

6

ConfigSpiBusy

R

Configuration interface busy

0b1: ConfigSpiBusy, Wait for ready until

next access to CfgPrmUpdDatReg

0b0: ConfigSpiReady, CfgPrmUpdDatReg

can be accessed

-

-

-

5...

2

-

-

reserved

undef

-

-

1

ReadCmdSelect

R

Read type of read command for SPI-flash

0b1: SpiReadTypeStandard, Standard Spi

read command is used

0b0: SpiReadTypeFast, Fast Spi read

command is used

-

-

-

0

SpiCsSet

RorW

Chip Select at SPI interface to serial

configuration prom

0b1: SpiCsSetHigh, Write: Drive SPI Chip

Select line high

0b0: SpiCsSetLow, Write: Drive SPI Chip

Select line low, possible only if enabled by

CodePrgIfEn

0b0: SpiCsIsHigh, Read: Status of SPI Chip

Select line is high

0b0: SpiCsIsLow, Read: Status SPI Chip

Select line is low

0b1

X

-