Ext fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 320

EXT FPGA

ARTM-831X Installation and Use (6806800M76E)

320

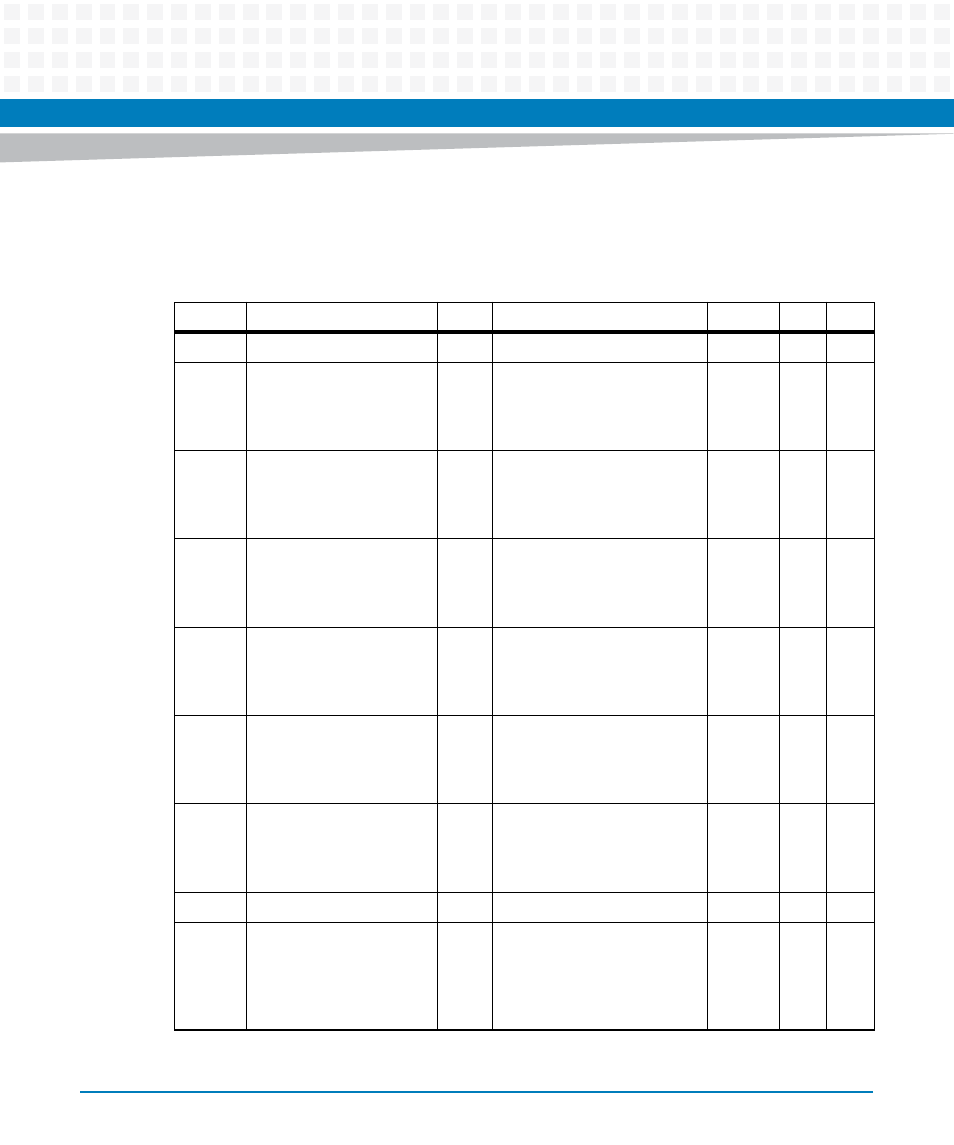

The bits of this register reset the respective bits in Xrt75LineEvtReg. Writing a 1 to a bit in

Xrt75LineEvtResReg resets the corresponding bit in Xrt75LineEvtReg. The interrupt bit in

Xrt75LineEvtReg is kept reset until writing a 0 to the corresponding bit in Xrt75LineEvtResReg

re-enables its monitor function again.

Bit

Acronym

Type

Description

Default

Pwr

Soft

31...22

-

-

reserved

undef

-

-

21

Xrt75TrmDmoIntrptRese

t5

RW

0b1:

Xrt75TrmDmoIntrptReset5,

resets Transmitter Drive

Monitor of line 5 indicator bit

0b0

X

X

20

Xrt75TrmDmoIntrptRese

t4

RW

0b1:

Xrt75TrmDmoIntrptReset4,

resets Transmitter Drive

Monitor of line 4 indicator bit

0b0

X

X

19

Xrt75TrmDmoIntrptRese

t3

RW

0b1:

Xrt75TrmDmoIntrptReset3,

resets Transmitter Drive

Monitor of line 3 indicator bit

0b0

X

X

18

Xrt75TrmDmoIntrptRese

t2

RW

0b1:

Xrt75TrmDmoIntrptReset2,

resets Transmitter Drive

Monitor of line 2 indicator bit

0b0

X

X

17

Xrt75TrmDmoIntrptRese

t1

RW

0b1:

Xrt75TrmDmoIntrptReset1,

resets Transmitter Drive

Monitor of line 1 indicator bit

0b0

X

X

16

Xrt75TrmDmoIntrptRese

t0

RW

0b1:

Xrt75TrmDmoIntrptReset0,

resets Transmitter Drive

Monitor of line 0 indicator bit

0b0

X

X

15...14

-

-

reserved

undef

-

-

13

Xrt75RcvLoLIntrptReset5

RW

0b1:

Xrt75RcvLoLIntrptReset5,

resets Receiver Line 5

indicates loss of lock

indicator bit

0b0

X

X