Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 177

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

177

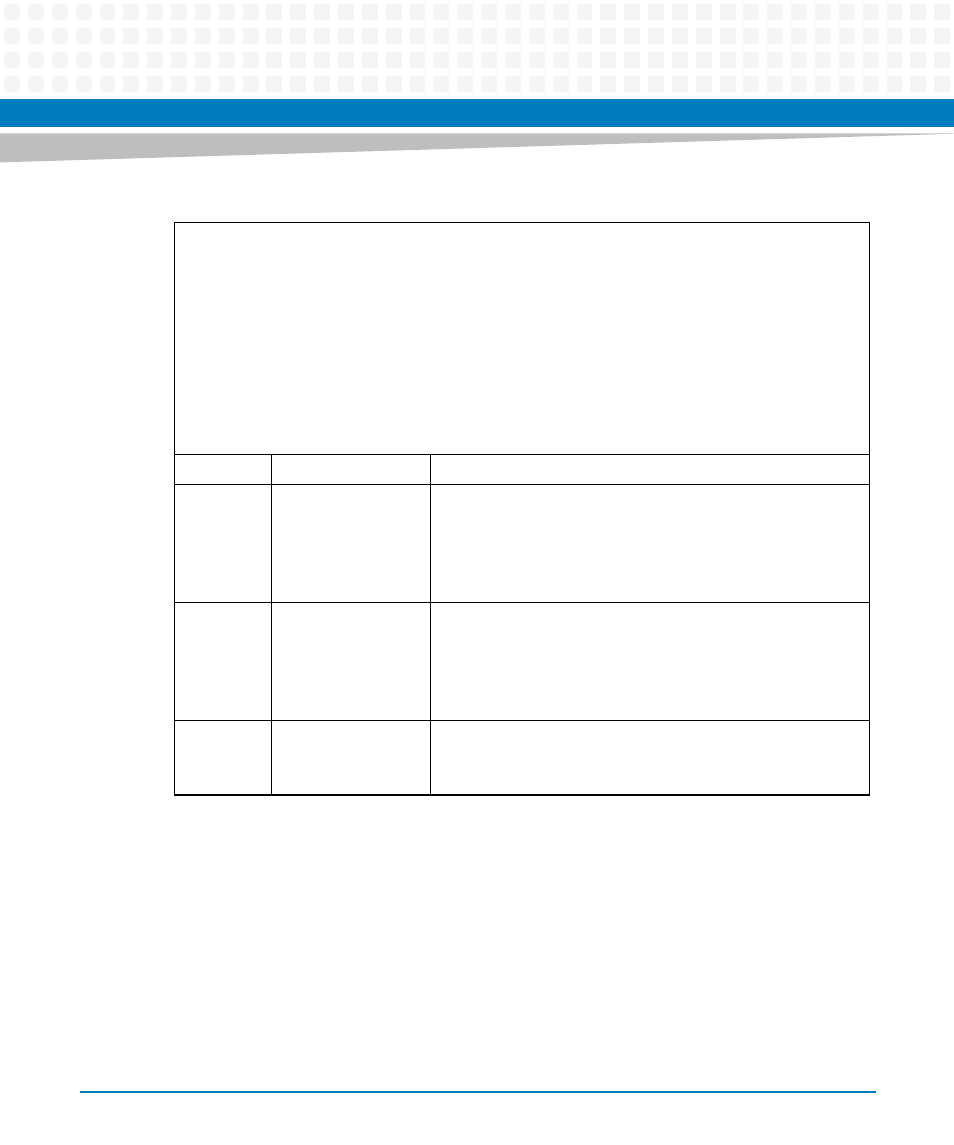

TSI Interior/Exterior Test Pattern Generator Block (TsiTstPatGenBlk) [Hw: Cy1, InR, OutR]

The TstPatGen generates a pseudo random binary sequence with the aid of a 11-bit LFSR (feedback

taps on stage nine and eleven). Alternatively a static pattern can be inserted.

In case of the Interior (Regs have indize 0) generator it substitutes the incoming data in a timeslot to

the TSI.

In case of the Exterior (Regs have indize 1) generator it substitutes an outgoing data of a timeslot of

the TSI.

The TSI timeslot is selectable between 0 and 65535.

Access via PCI-bus 512kByte non-prefetchable memory area of 64bit-bar[3,2], hereof assigned to this

block: 1080...10BF

Address

Acronym

Description

0x1080

0x1090

TstPatGenTsReg0

TstPatGenTsReg1

Test Pattern Generator Timeslot Register (16bit) [Hw: asyn,

WAck4, RAck4]

This registers specifies the incoming (Int) or outgoing (Ext) TSI

timeslot(0 ... 65535) to be substituted by generator pattern.

0x1082

0x1092

TstPatGenDatReg0

TstPatGenDatReg1

Test Pattern Generator Data Register (8bit) [Hw: asyn, WAck4,

RAck4]

This registers provides the test pattern to be transmitted in the

case of static pattern transmission.

Not used in the case of pseudo random pattern transmission.

0x1083

0x1093

TstPatGenCtrlReg0

TstPatGenCtrlReg1

Test Pattern Generator Control Register (8bit) [Hw: asyn,

WAck4, RAck4]

This registers controls test pattern transmission

Table 9-5 RTM FPGA Address map Overview (continued)