Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 182

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

182

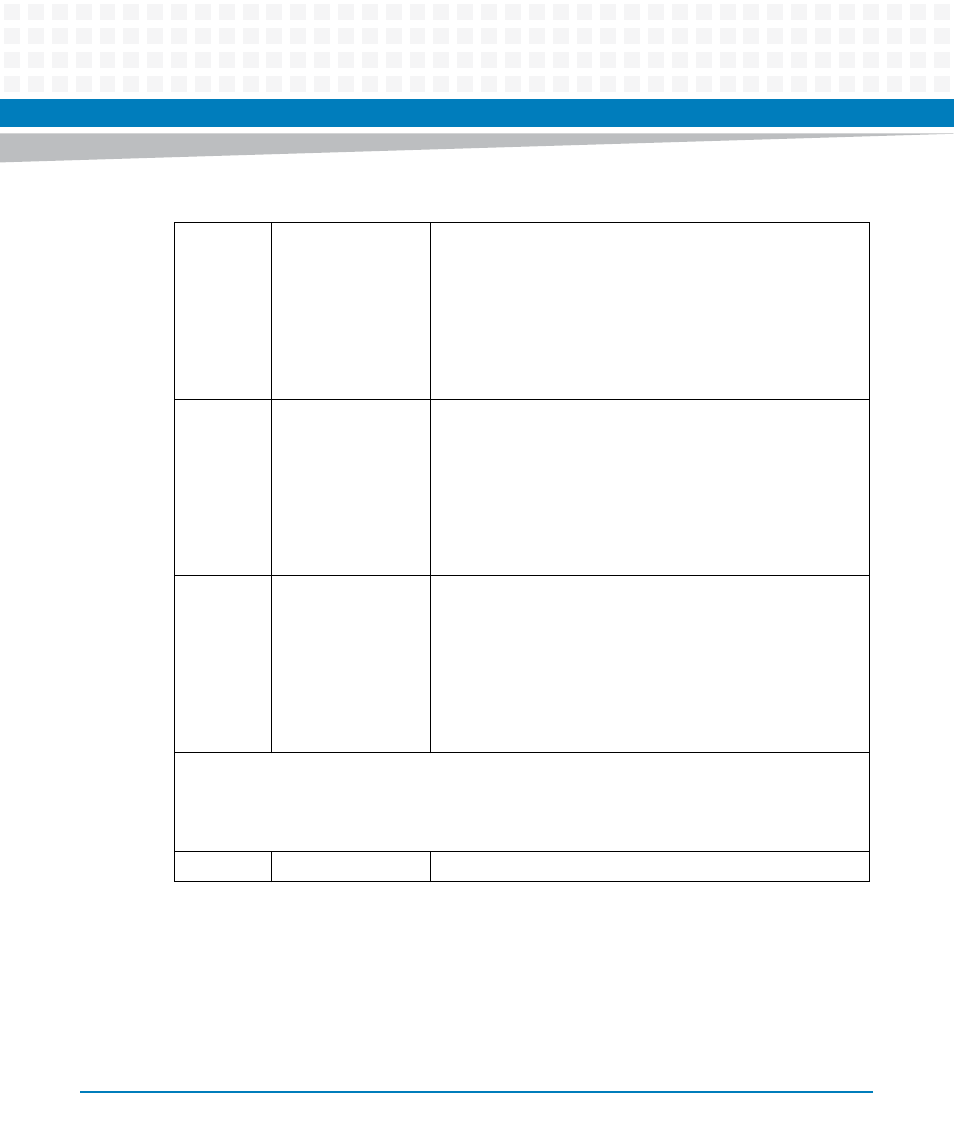

0x120C

0x124C

0x128C

SupplTstPatErrCntRe

g0

SupplTstPatErrCntRe

g1

SupplTstPatErrCntRe

g2

Deserializer Supplemental Test Pattern Error Count Register

(32bit) [Hw: asyn, WAck4, RAck4]

This register indicates the number of the test pattern errors

since starting the static pattern reception by the

ErrCntCtrlReg:SupplTstPatErrCntStart bit. The counter sticks at

0xFFFF_FFFF.

Reg0 is for Serdes-connection to the BaseBoard, Reg1 to DMC1

and Reg2 to DMC2.

0x1210

0x1250

0x1290

CrcErrCntReg0

CrcErrCntReg1

CrcErrCntReg2

Deserializer CRC Error Count Register (32bit) [Hw: asyn,

WAck4, RAck4]

This register indicates the number of the CRC errors since

enabling the CRC error counting by the

ErrCntCtrlReg:CrcErrCntStart bit. The error counter sticks at

0xFFFFFF.

Reg0 is for Serdes-connection to the BaseBoard, Reg1 to DMC1

and Reg2 to DMC2.

0x1214

0x1254

0x1294

DispErrCntReg0

DispErrCntReg1

DispErrCntReg2

Deserializer Disparity Error Count Register (32bit) [Hw: asyn ,

WAck4, RAck4]

This register indicates the number of the Disparity errors since

enabling the Disparity error counting by the

ErrCntCtrlReg:DispErrCntStart bit. The error counter sticks at

0xFFFFFF.

Reg0 is for Serdes-connection to the BaseBoard, Reg1 to DMC1

and Reg2 to DMC2.

Transport Overhead Registers (TohRegs) [Hw: Cy1, InR, OutR]

Transport Overhead Registers for E1,2 and D1..12 DCCbytes insertion/extraction

Access via PCI-bus 512kByte non-prefetchable memory area of 64bit-bar[3,2], hereof assigned to this

block: 1300...13FF

Address

Acronym

Description

Table 9-5 RTM FPGA Address map Overview (continued)