Tsi fpga, 15component event status reset register – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 247

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

247

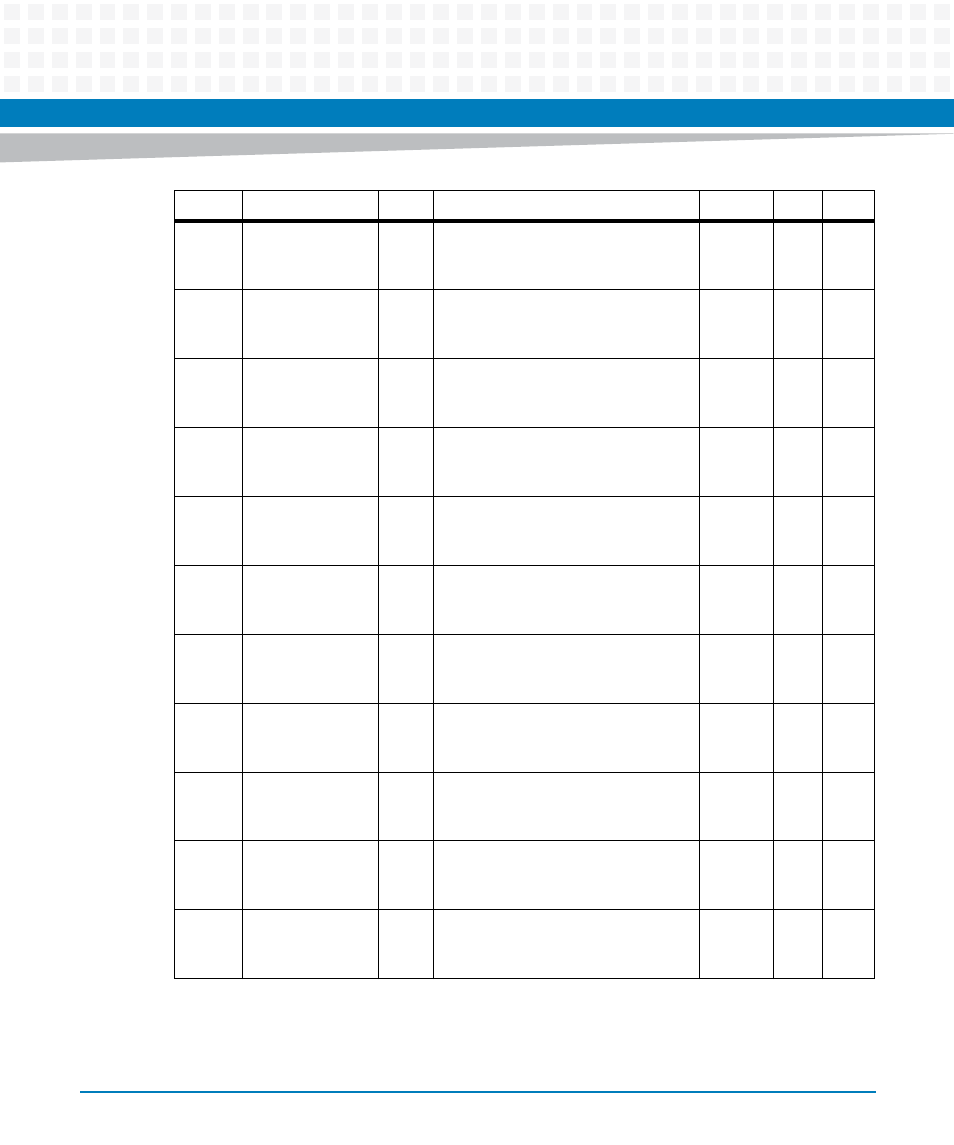

9.5.2.11.15Component Event Status Reset Register

Address:

10

Xrt75ChpIntrpt2

R

0b1: Xrt75ChpIntrpt2, active if the

Xrt75 line interface unit 2 has

signalled an interrupt

0b0

F

F

9

Xrt75ChpIntrpt1

R

0b1: Xrt75ChpIntrpt1, active if the

Xrt75 line interface unit 1 has

signalled an interrupt

0b0

F

F

8

Xrt75ChpIntrpt0

R

0b1: Xrt75ChpIntrpt0, active if the

Xrt75 line interface unit 0 has

signalled an interrupt

0b0

F

F

7

Xrt86ChpIntrpt5

R

0b1: Xrt86ChpIntrpt5, active if the

Xrt86 framer 5 has signalled an

interrupt

0b0

F

F

6

Xrt86ChpIntrpt4

R

0b1: Xrt86ChpIntrpt4, active if the

Xrt86 framer 4 has signalled an

interrupt

0b0

F

F

5

Xrt86ChpIntrpt3

R

0b1: Xrt86ChpIntrpt3, active if the

Xrt86 framer 3 has signalled an

interrupt

0b0

F

F

4

Xrt86ChpIntrpt2

R

0b1: Xrt86ChpIntrpt2, active if the

Xrt86 framer 2 has signalled an

interrupt

0b0

F

F

3

Xrt86ChpIntrpt1

R

0b1: Xrt86ChpIntrpt1, active if the

Xrt86 framer 1 has signalled an

interrupt

0b0

F

F

2

Xrt86ChpIntrpt0

R

0b1: Xrt86ChpIntrpt0, active if the

Xrt86 framer 0 has signalled an

interrupt

0b0

F

F

1

Pmc83ChpIntrpt

1

R

0b1: Pmc83ChpIntrpt1, active if the

Pmc8310 framer 1 has signalled an

interrupt

0b0

F

F

0

Pmc83ChpIntrpt

0

R

0b1: Pmc83ChpIntrpt0, active if the

Pmc8310 framer 0 has signalled an

interrupt

0b0

F

F

Bit

Acronym

Type

Description

Default

Pwr

Soft