Ext fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 297

EXT FPGA

ARTM-831X Installation and Use (6806800M76E)

297

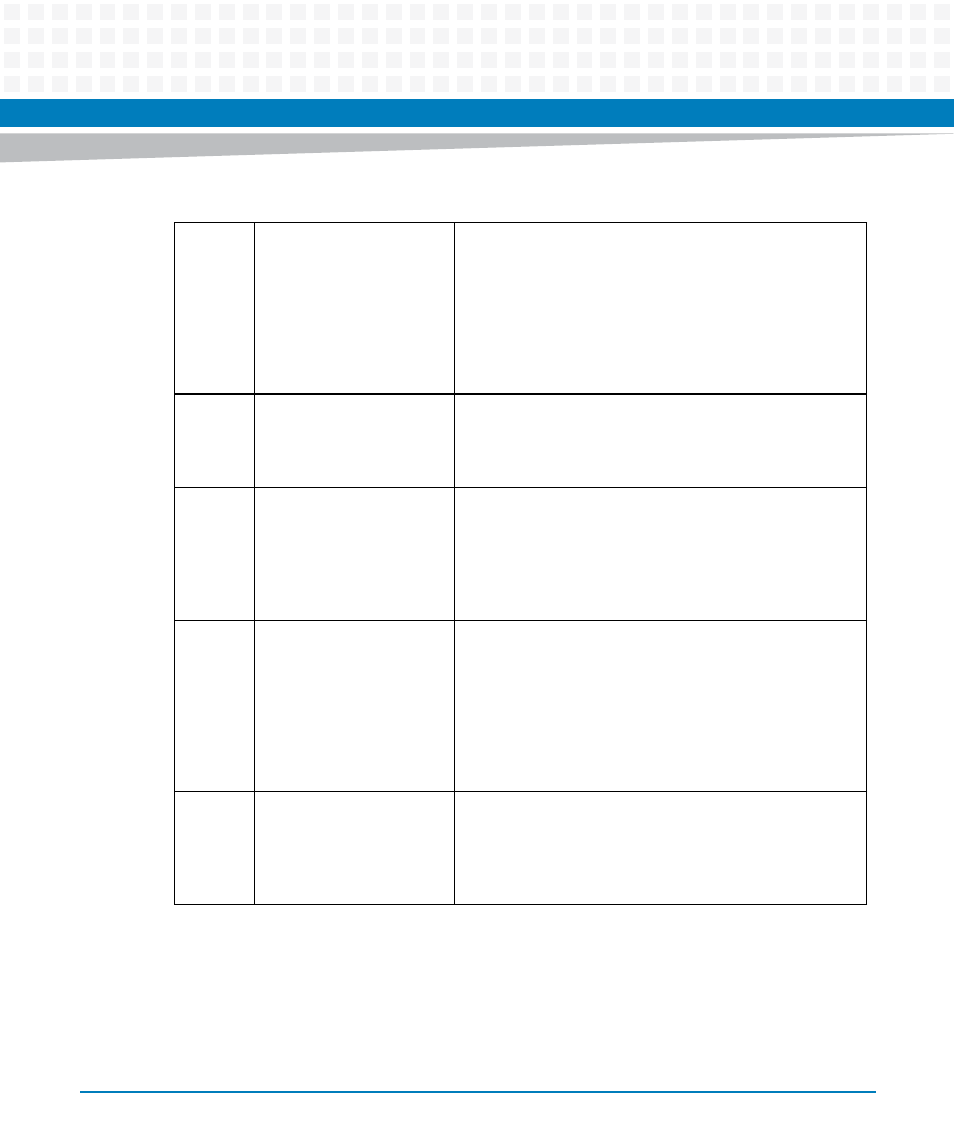

0x14

CompEvtResReg

Component Event Status Reset Register (8bit) [Hw: syn,

WAck1, RAck1]

The bits of this register reset the respective bits in

CompEvtReg. Writing a 1 to a bit in CompEvtResReg resets

the corresponding bit in CompEvtReg The interrupt bit in

CompEvtReg is kept reset until writing a 0 to the

corresponding bit in CompEvtResReg re-enables its

monitor function.again.

0x18

CompEvtMaskReg

Component Event Status Mask Register (8bit) [Hw: syn,

WAck1, RAck1]

The bits of this register mask the bits of the CompEvtReg.

for the generation of a Interrupt (MSI) to the host via PCIE.

0x20

Xrt86LineEvtReg

Xrt86 Framer Line Event Status Register (32bit ) [Hw: syn,

WAck1, RAck1]

This register monitor the loss of signal outputs of the Xrt86

framer chips 2..5. If a loss of signal occurs, the respective bit

is set. It can be reset by writing the respective bit in

Xrt86LineEvtResReg.

0x24

Xrt86LineEvtResReg

Xrt86 Framer Line Event Status Reset Register (32bit) [Hw:

syn, WAck1, RAck1]

The bits of this register reset the respective bits in

Xrt86LineEvtReg. Writing a 1 to a bit in

Xrt86LineEvtResReg resets the corresponding bit in

Xrt86LineEvtReg The interrupt bit in Xrt86LineEvtReg is

kept reset until writing a 0 to the corresponding bit in

Xrt86LineEvtResReg re-enables its monitor function.again.

0x28

Xrt86LineEvtMaskReg

Xrt86 Framer Line Event Status Mask Register (32bit) [Hw:

syn, WAck1, RAck1]

The bits of this register mask the bits of the

Xrt86LineEvtReg. For the generation of an interrupt to the

host.

Table 10-4 EXT FPGA Addressmap Overview (continued)