Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 181

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

181

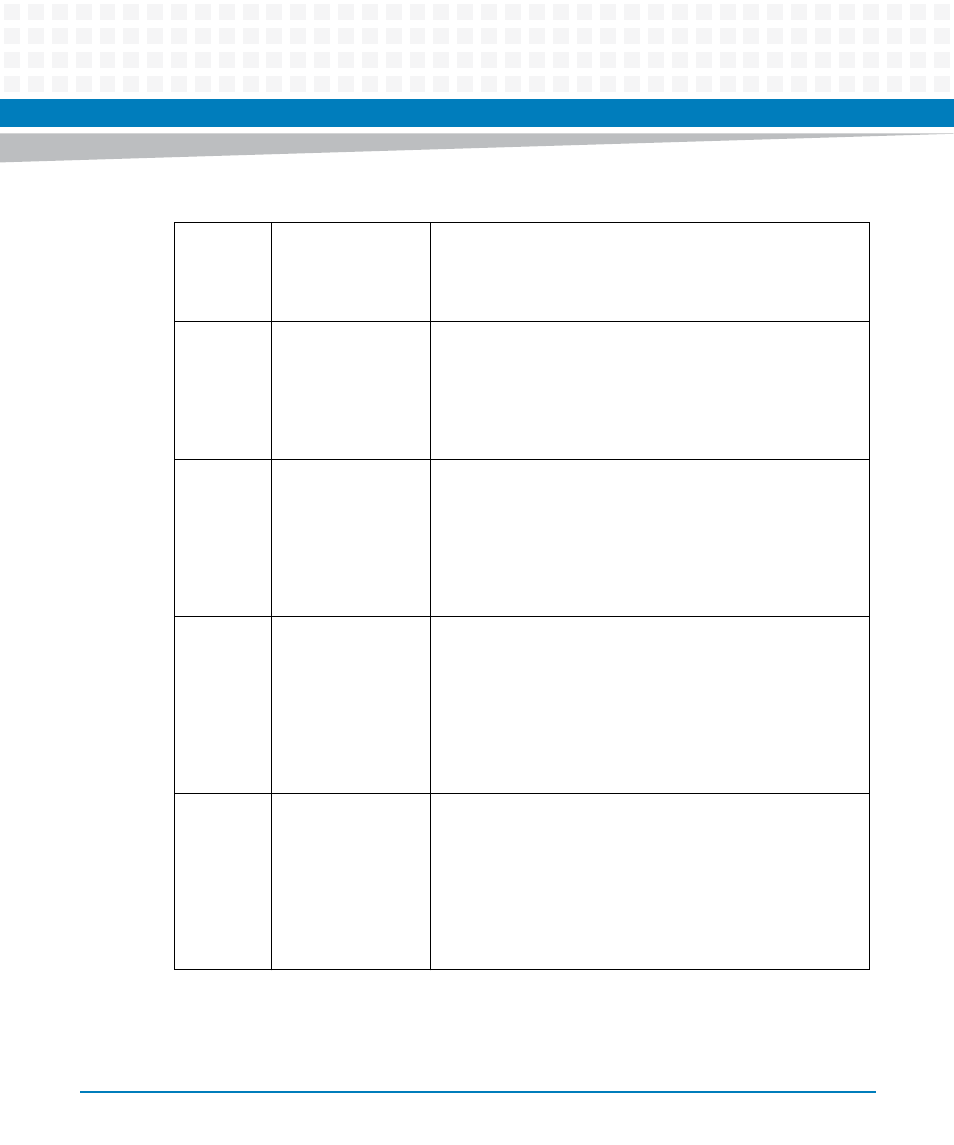

0x1201

0x1241

0x1281

SerDesRcvStatReg0

SerDesRcvStatReg1

SerDesRcvStatReg2

Serdes Receiver Status Register (8bit) [Hw: syn, WAck1 , RAck1]

The Serdes transmitter status is shown.

Reg0 is for Serdes-connection to the BaseBoard, Reg1 to DMC1

and Reg2 to DMC2.

0x1202

0x1242

0x1282

SupplTstPatDataRcv

DatReg0

SupplTstPatDataRcv

DatReg1

SupplTstPatDataRcv

DatReg2

Supplemental Test Pattern Receive Data Register (16bit) [Hw:

asyn, WAck4, RAck4]

This register provides the received test pattern from the

supplementary channel.

Reg0 is for Serdes-connection to the BaseBoard, Reg1 to DMC1

and Reg2 to DMC2.

0x1204

0x1244

0x1284

SupplTstPatDataCm

pDatReg0

SupplTstPatDataCm

pDatReg1

SupplTstPatDataCm

pDatReg2

Supplemental Test Pattern Compare Data Register (16bit) [Hw:

asyn, WAck4, RAck4]

This register determines the data the received test pattern

from the supplementary channel are compared to for error

counting.

Reg0 is for Serdes-connection to the BaseBoard, Reg1 to DMC1

and Reg2 to DMC2.

0x1206

0x1246

0x1286

ErrCntCtrlReg0

ErrCntCtrlReg1

ErrCntCtrlReg2

Test Pattern, CRC and Disparity Error Counter Control Register

(8bit) [Hw: asyn, WAck4, RAck4]

This register controls the error counter of static test pattern

received via the supplementary channel, it controls the error

counter for CRC error rate evaluation and the counter totally

transferred frame counter.

Reg0 is for Serdes-connection to the BaseBoard, Reg1 to DMC1

and Reg2 to DMC2.

0x1208

0x1248

0x1288

TstFrameCntReg0

TstFrameCntReg1

TstFrameCntReg2

Test Frame Count Register (32bit) [Hw: asyn, WAck4, RAck4]

This register indicates the number of 125 μs frames since

starting the frame sync counting by

ErrCntCtrlReg:FrameCntStart bit. During 125 μs one SerDes

frame is received. Each frame contains a static test pattern and

a CRC checksum.

Reg0 is for Serdes-connection to the BaseBoard, Reg1 to DMC1

and Reg2 to DMC2.

Table 9-5 RTM FPGA Address map Overview (continued)