4 ext fpga hw/sw interfaces, 1 ext fpga addressmap overview, Table 10-4 – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 296: Ext fpga addressmap overview, Ext fpga

EXT FPGA

ARTM-831X Installation and Use (6806800M76E)

296

10.4 EXT FPGA HW/SW Interfaces

10.4.1 EXT FPGA Addressmap Overview

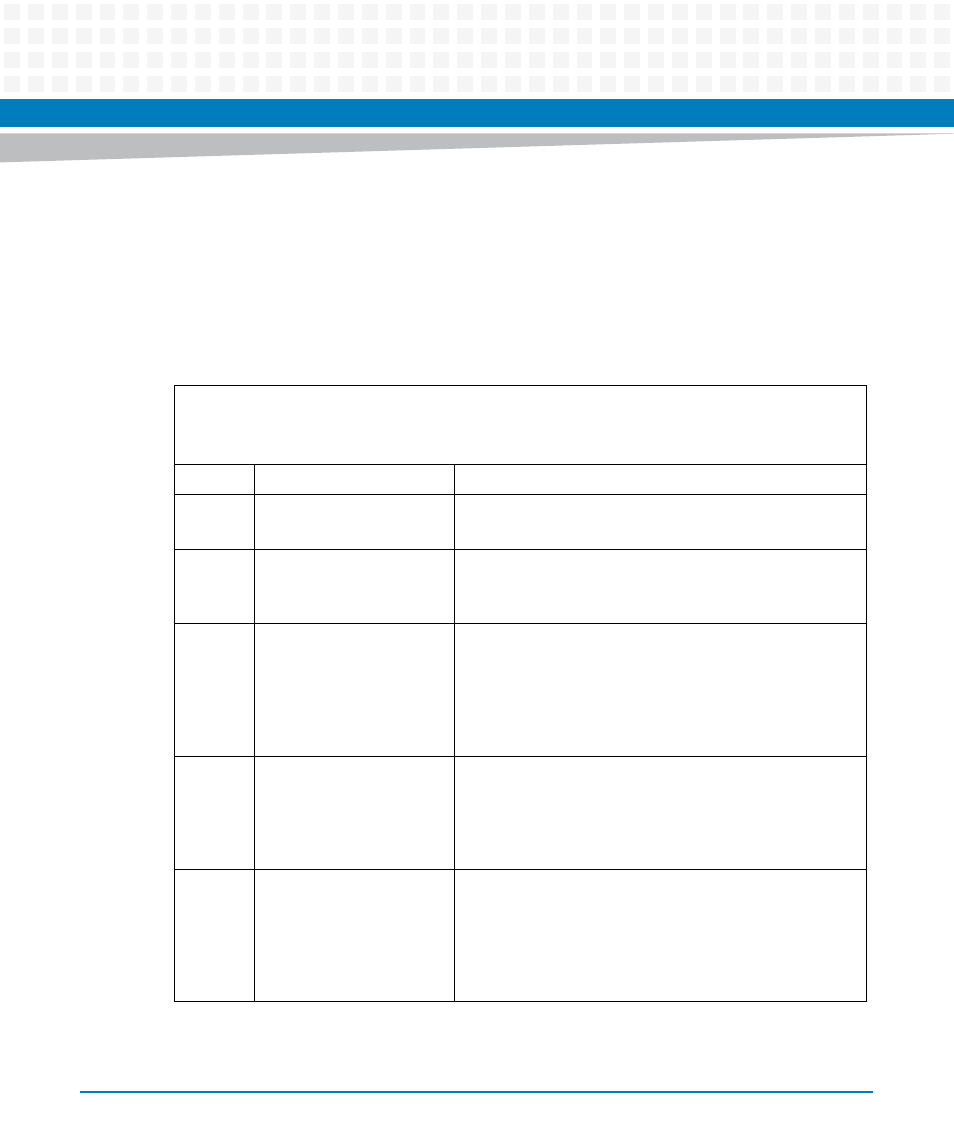

Table 10-4 EXT FPGA Addressmap Overview

General Register (GnrlRegs) [Hw: Cy]

Collection of general register not dedicated to particular functions

Access via Spi-bus 256Byte memory area, hereof assigned to this block: 0...8F

Address

Acronym

Description

0x0

SoftResReg

Soft Reset Register (32bit) [Hw: syn, WAck1, RAck1, WTP]

Brings by SoftReset affected registers to power up state

0x4

ExtFpgaVerReg

ExtFpga Version Register (32bit) [Hw: syn, WAck1, RAck1]

The version of the ExtFpga determined by compilation is

read.

0x8

RtmMatchExtFpgaVerReg

Matching TSI-FPGA Version Register (32bit) [Hw: syn,

WAck1, RAck1]

The version of the matching ExtFpga (since ExtFpga

extends TSI-FPGA) is read. Must match always exactly the

version in RtmMatchExtFpgaVerReg within ExtFpga

determined by compilation

0xC

ModulTypeFnctReg

Module Type and Functional Revision Register (32bit) [Hw:

syn, WAck1, RAck1]

The module type and functional revision of the module the

Fpga is upon. The value is determined by pull-up/pulldown

resistors.

0x10

CompEvtReg

Component Event Status Register (8bit) [Hw: syn, WAck1,

RAck1]

This register monitors the internal components, eg. Xrt86

framer interrupt status and alarm pins. If an interrupt

occurs, the respective bit is set. It can be reset by writing

the respective bit in CompEvtReg.