3 registers, Table 8-21, Other configuration signals – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 128: Table 8-22, Register default, Base artm fpga

Base ARTM FPGA

ARTM-831X Installation and Use (6806800M76E)

128

8.3

Registers

For register Description, the convention shown in

Register Default and

Register Access Type are used.

BUSY/SISPI

O

SPI Master output Slave input during

configuration for SPIm mode, In user mode

used as output for SPI flash data. Signal

CONF_SPI_MOSI

D[0]/SPIFASTN

I

Select read command for SPI and SPIm modes.

External Pull-up required to select the Read op-

code 0x03 (standard read)

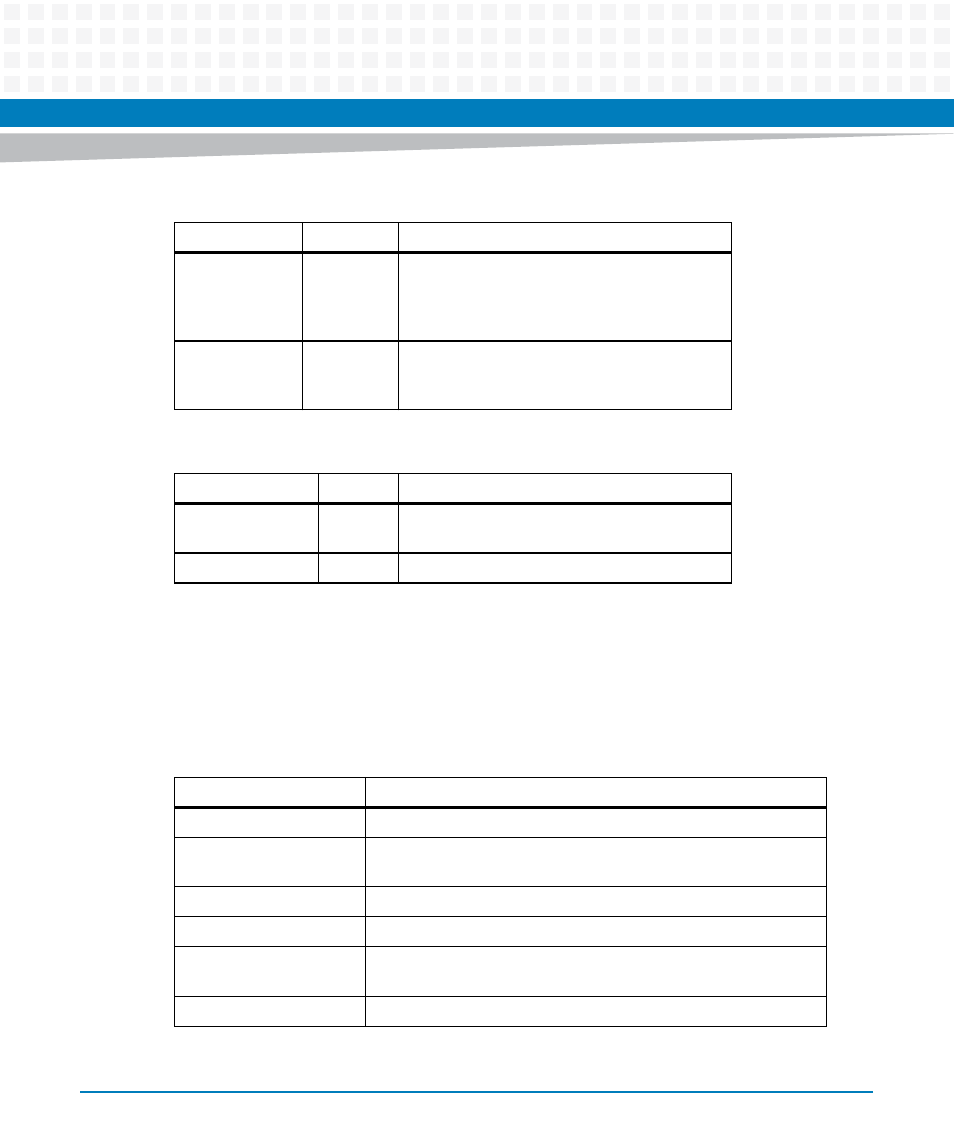

Table 8-21 Other Configuration Signals

Signal Name

Type

Description

CONF_CRC_ERR

O

Configuration Error. FPGA SRAM content is

corrupt.

FORCE_GOLDEN

I

Force Golden Image for ARTM Base FPGA

Table 8-20 Dual-Purpose Configuration Signals (continued)

Signal Name

Type

Description

Table 8-22 Register Default

Default

Description

-

Not applicable or undefined

0 or 1

Default value after SPP_RTM_RST_ is valid or after warm or cold

reset deassertion.

Undef.

Undefined value

Default value after deassertion of the reset signal

cold reset: 0 or 1

Default value after SPP_RTM_RST_ is valid or cold reset

deassertion. Warm reset don't modify the register content

Ext.

External Reset Source. Default depends on external logic level.