Table 8-54, Artm telecom clock monitor preselect register, Table 8-55 – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 148: Artm telecom clock monitor select register, Table 8-56, Artm telecom clock monitor control register, Base artm fpga

Base ARTM FPGA

ARTM-831X Installation and Use (6806800M76E)

148

15

CLK_T3_BITS

TDM T3 BITS Clock to Zone 3

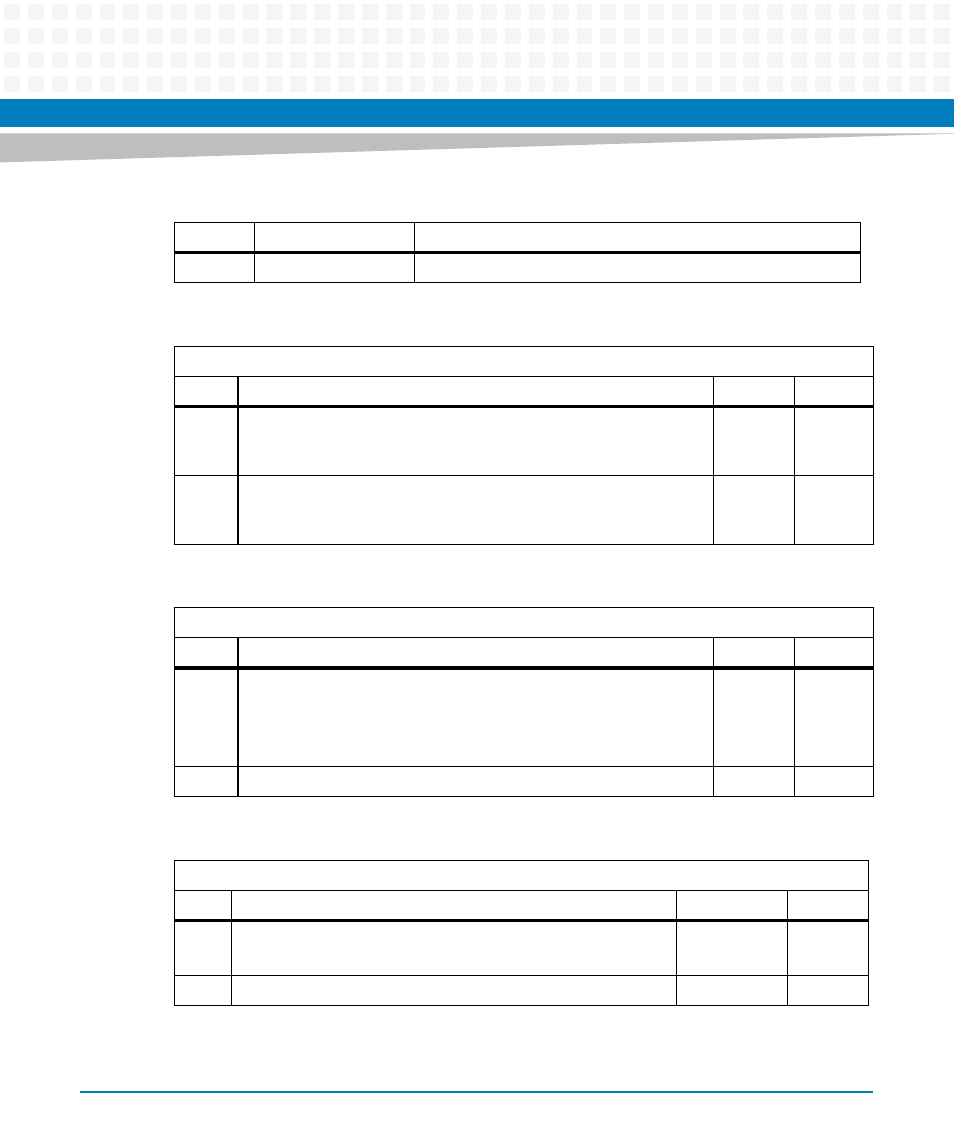

Table 8-54 ARTM Telecom Clock Monitor Preselect Register

Address: 0x20

Bit

Description

Default

Access

3:0

ClockMonitorPreselect_1. Preselect supervised ARTM Telecom

Clocks for clk_mon_1. See Table Preselected Telecom Clocks

Reference List

0

RTM: r/w

7:4

ClockMonitorPreselect_2. Preselect supervised ARTM Telecom

Clocks for clk_mon_2. See Table Preselected Telecom Clocks

Reference List

0

RTM: r/w

Table 8-55 ARTM Telecom Clock Monitor Select Register

Address: 0x21

Bit

Description

Default

Access

3:0

Select supervised ARTM Telecom Clocks 0 to 3

0-1: Select corresponding clock. See Table Supervised ARTM

Telecom Clocks Reference List

2-15: Reserved

0

RTM: r/w

7:4

Reserved

0

r

Table 8-56 ARTM Telecom Clock Monitor Control Register

Address: 0x22

Bit

Description

Default

Access

1:0

Enable supervised Telecom Clocks 0 and 1.

Set corresponding bit enable monitoring.

RTM_RST_: 0

RTM: r/w

7:2

Reserved

0

r

Table 8-53 289Preselected Telecom Clocks Reference List (continued)

Number Name

Description