Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 175

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

175

0x40

SerDesPselReg

SerDesPreselect Register (8bit) [Hw: syn , WAck1, RAck1]

Preselects the SerDes Quad and Channel

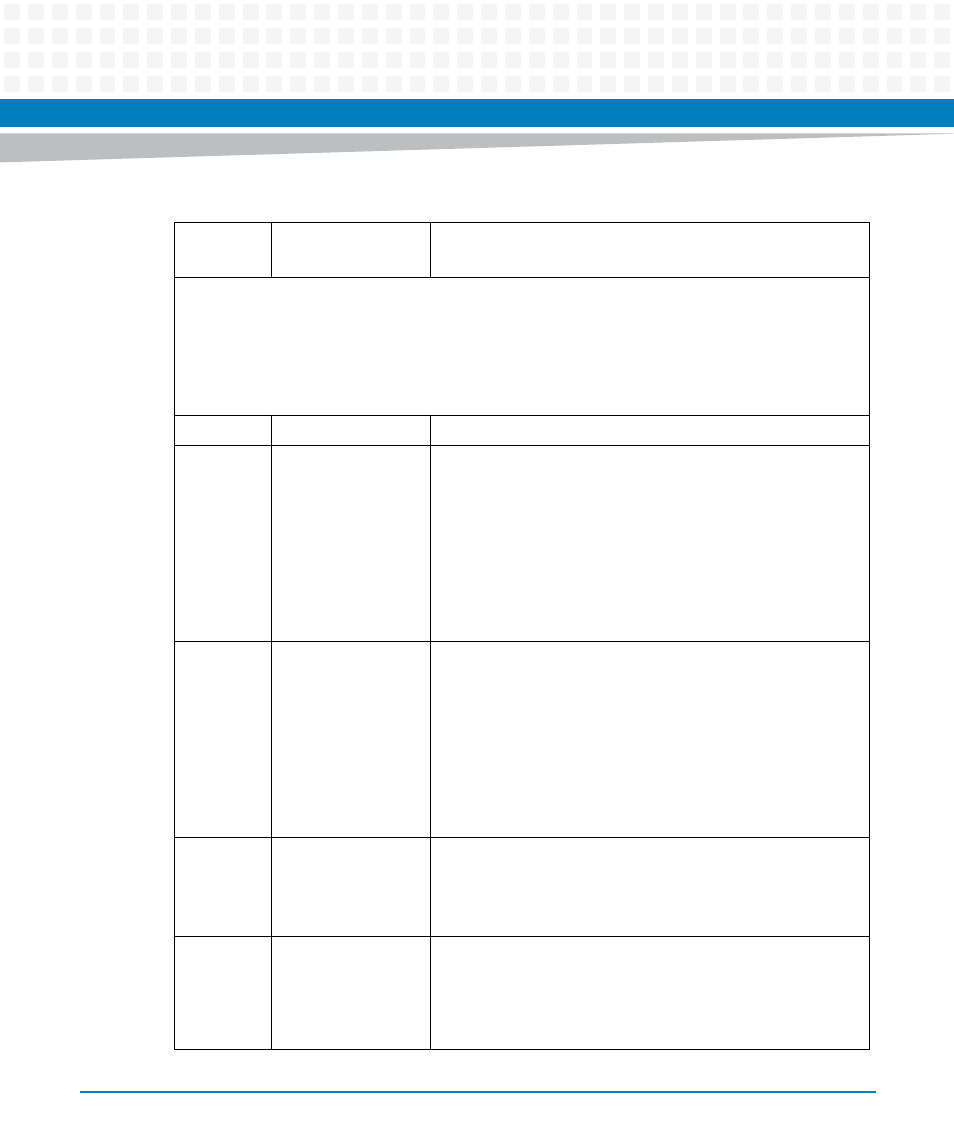

TSI Registers (TsiRegs) [Hw: Cy1, InR, OutR]

TSI Control and Status Registers to switch connections, initialize the connections by HW and monitor

initialization process, determine connection initialization value, determine data at Tsi channel 0 input,

monitor Tsi counter.

Access via PCI-bus 512kByte non-prefetchable memory area of 64bit-bar[3,2], hereof assigned to this

block: 1000...103F

Address

Acronym

Description

0x1000

TsiInitReg

Tsi Initialization Register (32bit) [Hw: syn, WAck1, RAck1, WRP

]

The TsiCnctRegs are written with 0x0000 from TsiInitValReg

during the first 250us after power-on reset, thus connecting all

output channels to input channel 0. All output channels carry

then as speech data the value from TsiCh0SpchDataReg (too

0x00 after power-on). The initialization process can be

monitored with TsiInitMonReg.

0x1004

TsiInitMonReg

Tsi Initialization Monitor Register (32bit) [Hw: syn, WAck1,

RAck1]

The TsiCnctRegs are written with 0x0000 from TsiInitValReg

during the first 250us after power-on reset, thus connecting all

output channels to input channel 0. All output channels carry

then as speech data the value from TsiCh0InpDatlReg (too 0x00

after power-on). This initialization takes between 125 and

250us and can be monitored.

0x1008

TsiInitValReg

Tsi Initialization Value Register (32bit) [Hw: syn, WAck1, RAck1]

The TsiCnctRegs are written with the value of this register when

initialization is started by TsiInitReg

0x100C

TsiCh0InpDatReg

Tsi Channel 0 Input Data Register (32bit) [Hw: asyn, WAck4,

RAck4]

The input channel 0 of the Tsi is connected to this

registerCnctRegs are written with the value of this register

when initialization is started by TsiInitReg

Table 9-5 RTM FPGA Address map Overview (continued)