9 deserializer to tsi allocater block (des2tsiblk), Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 219

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

219

9.5.2.9

Deserializer to TSI Allocater Block (Des2TsiBlk)

Resets:

Pwr = Power On Reset

Soft = Soft Reset

The Tsi2SerBlk contains 3 converter blocks from Serdes links of DspFpgas. Each converter can

put the payload information of up to 30720 from DspFpga at the opposite side to incoming

timeslots of the TSI.

The received supplemental channel test pattern data can be read by using the registers of this

block. Furthermore the CRC status signals from the SerDes IP Block are evaluated and CRC and

Disparity errors are counted and indicated. The the link synchronization is controlled by

registers of this block too.

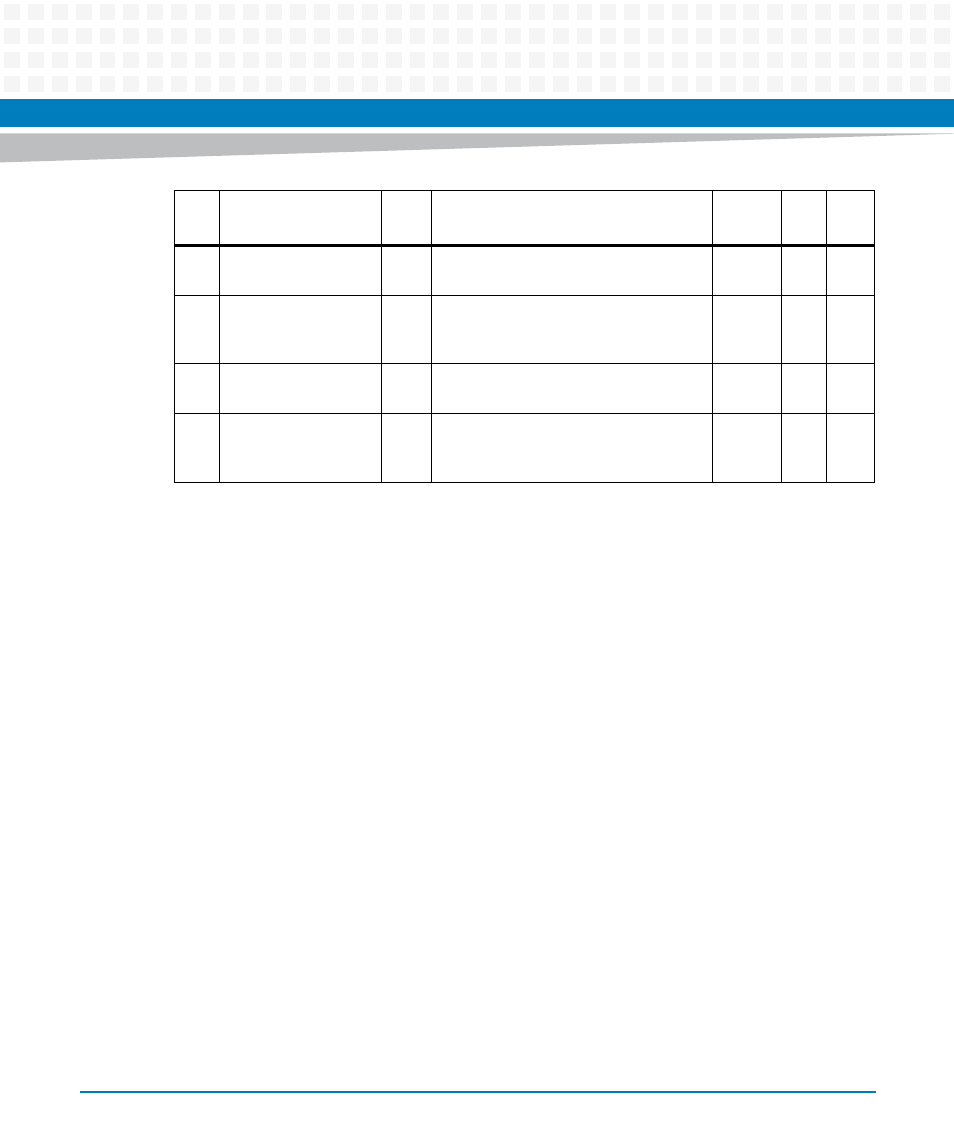

9.5.2.9.1 Serdes Receiver Control Register

Addresses:

0x1200, SerDesRcvCtrlReg0

0x1240, SerDesRcvCtrlReg1

0x1280, SerDesRcvCtrlReg2

Width: 8 bit

3

CrcGenConErrPrvk

RW

0b1: CrcGenContErrPrvk, errors are

inserted continuously

0b0

X

X

2

CrcGenSingleErrPrvk

RW

0b1: CrcGenSinglErrPrvk, one error is

inserted when the bit changes from 0

to 1

0b0

X

X

1

DispGenContErrPrvk

RW

0b1: DispGenContErrPrvk, errors are

inserted continuously

0b0

X

X

0

DispGenSingleErrPrv

k

RW

0b1: DispGenSingleErrPrvk, one error is

inserted when the bit changes from 0

to 1

0b0

X

X

Bit

Acronym

Type

Description

Default

Pwr

Soft