Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 260

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

260

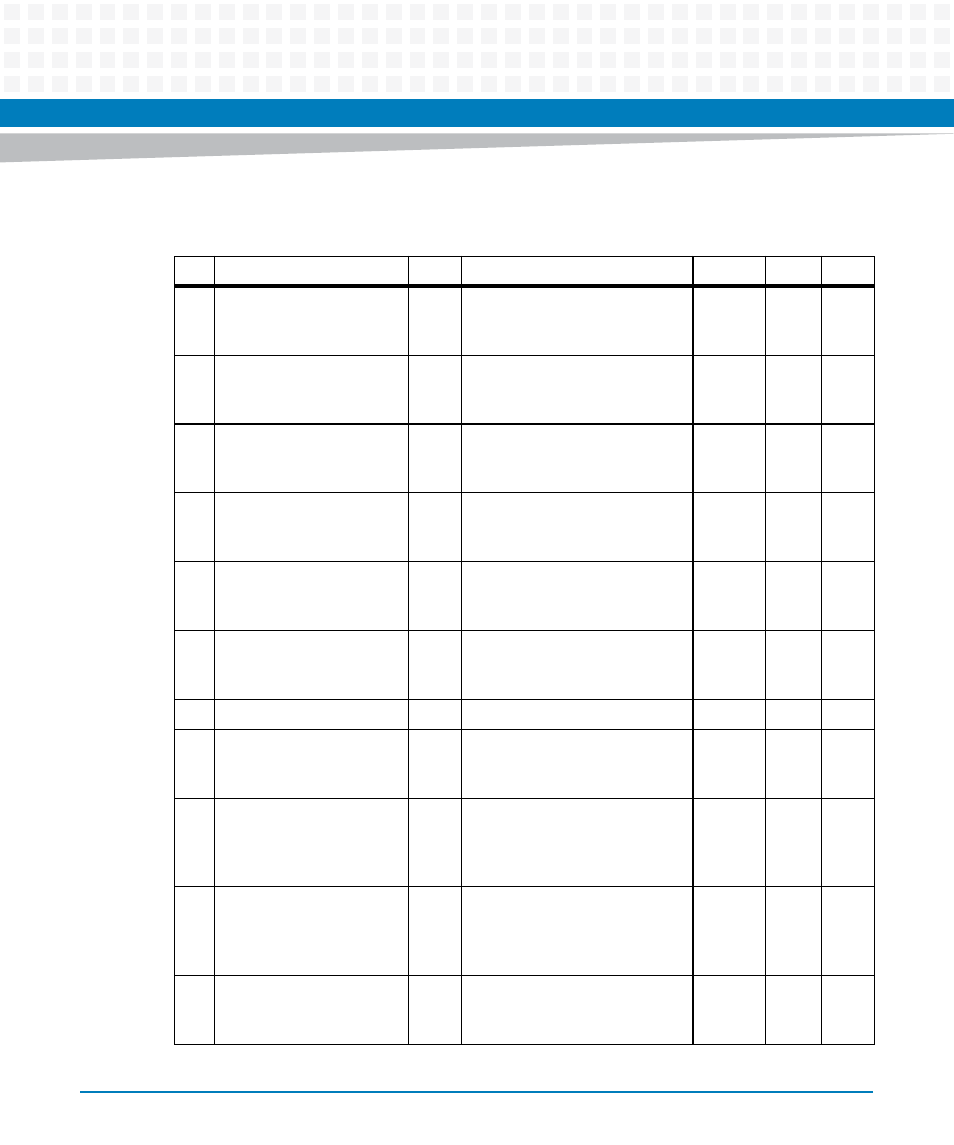

Allows to simulate several faults initiated not by the original source but by the host SW for test

purposes

Bit

Acronym

Type

Description

Default

Pwr

Soft

31

SerdesCltIfIntrptForce3

RW

0b1: SerdesCltIfIntrptForce3,

force Interrupt from Serdes

Quad3 indicator

0b0

X

X

30

SerdesCltIfIntrptForce2

RW

0b1: SerdesCltIfIntrptForce2,

force Interrupt from Serdes

Quad2 indicator

0b0

X

X

29

SerdesCltIfIntrptForce1

RW

0b1: SerdesCltIfIntrptForce1,

force Interrupt from Serdes

Quad1 indicator

0b0

X

X

28

SerdesCltIfIntrptForce0

RW

0b1: SerdesCltIfIntrptForce0,

force Interrupt from Serdes

Quad0 indicator

0b0

X

X

27

Spi2BusRdyTmOutForce

RW

0b1: Spi2BusRdyTmOutForce,

force ready timeout at Spi bus 2

indicator

0b0

X

X

26

Spi1BusRdyTmOutForce

RW

0b1: Spi1BusRdyTmOutForce,

force ready timeout at Spi bus 1

indicator

0b0

X

X

25

-

-

reserved

undef

-

-

24

LcBusRdyTmOutForce

RW

0b1: LcBusRdyTmOutForce,

force ready timeout at local bus

indicator

0b0

X

X

23

ParErrDrpSbi1Force

RW

0b1: ParErrDrpSbi1Force, force

parity error in SBI drop data

from Sonet/Sdh-framer1

indicator

0b0

X

X

22

ParErrDrpSbi0Force

RW

0b1: ParErrDrpSbi0Force, force

parity error in SBI drop data

from Sonet/Sdh-framer0

indicator

0b0

X

X

21

SerdesRcvErrorForce2

RW

0b1: SerdesRcvErrorForce2,

force the serdes receiver2 error

indicator

0b0

X

X