Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 185

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

185

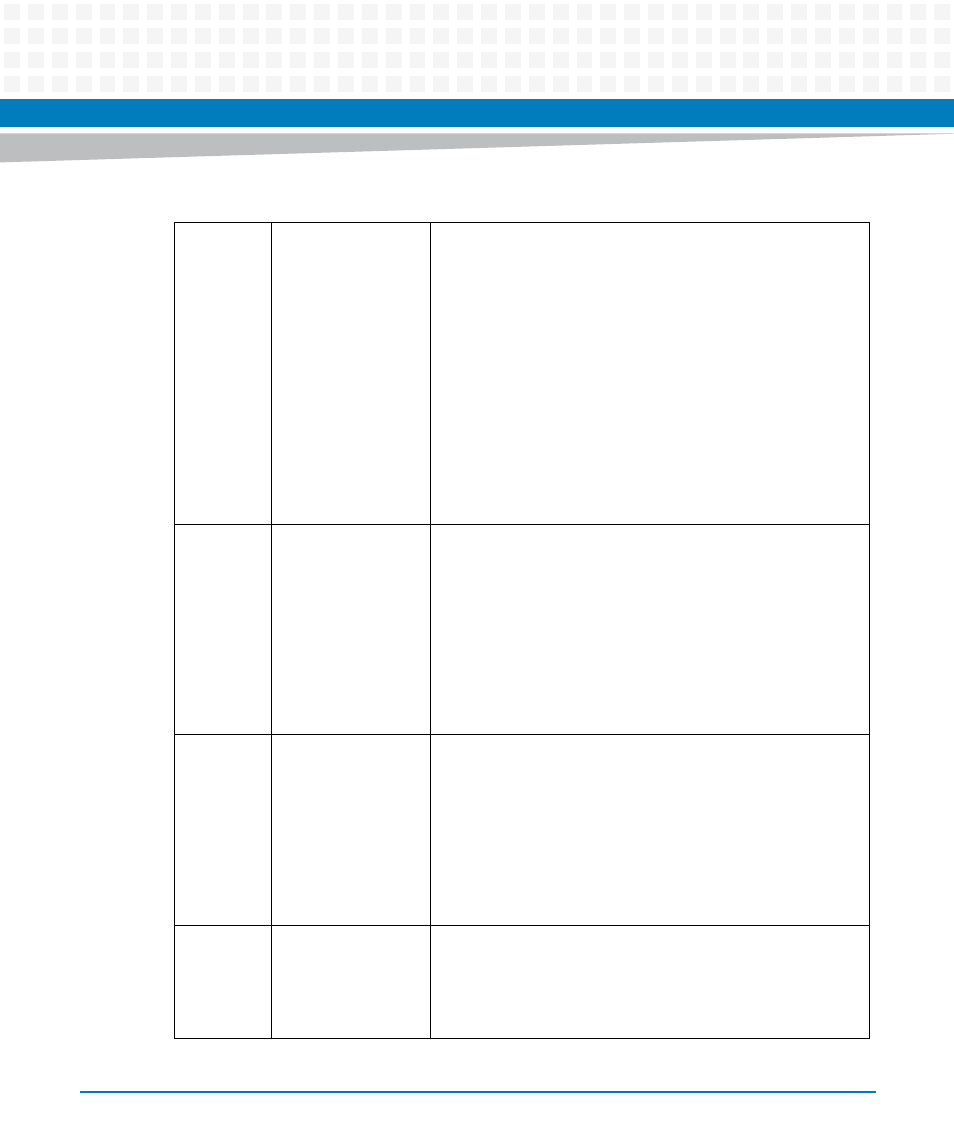

0x1430

0x1434

0x1438

0x143C

0x1440

0x1444

0x1448

0x144C

0x1450

0x1454

0x1458

0x145C

SyncSelReg00

SyncSelReg01

SyncSelReg10

SyncSelReg11

SyncSelReg20

SyncSelReg21

SyncSelReg30

SyncSelReg31

SyncSelReg40

SyncSelReg41

SyncSelReg50

SyncSelReg51

Synchronisation Select Register (32bit) [Hw: syn, WAck1,

RAck1]

These registers determine the superframe synchronization of

the exar framers: Ds1 Esf, Ds1 SF or E1 mode. Each HMVIP

interface of the framers is partitioned into two parts, which can

be synchronized separately. The first digit of the indize

numbers a framer chip and the second a partition of this framer

0x1460

PohPartnerMfsOffse

tReg

Path Overhead Partner Mfs Offset register (8bit) [Hw: syn,

WAck1, RAck1]

The bits of this register show if a valid partner multi-frame-sync

pulse is received via the path overhead interface of sonet/sdh

framer 0. Further the offset the received partner multi-frame-

sync pulse to the own framesync pulse is shown. The offset can

be 0 to 47 frames (125us), measured as distance behind the

own pulse. The received partner frame pulse is judged as valid,

if twopulses occur one time in the expected distance,

measured with the own 131.072 MHz clock.

0x1461

LvdsPartnerMfsOffse

tReg

Lvds Partner Mfs Offset register (8bit) [Hw: syn , WAck1, RAck1]

The bits of this register show if a valid partner multi-frame-sync

pulse is received via lvds link. Further the offset the received

partner multi-frame-sync pulse to the own framesync pulse is

shown. The offset can be 0 to 47 frames (125us), measured as

distance behind the own pulse. The received partner frame

pulse is judged as valid, if 2 pulses occur one time in the

expected distance, measured with the own 131.072 MHz

clock.

0x1470

CompResReg

Component Reset Register (32bit) [Hw: syn, WAck1, RAck1]

The bits of this register reset the respective internal and

external components, e.g. Xrt86 frame, etc. Writing a 1 to a bit

puts the respective component into reset, until writing a 0 re-

enables its function again.

Table 9-5 RTM FPGA Address map Overview (continued)