Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 233

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

233

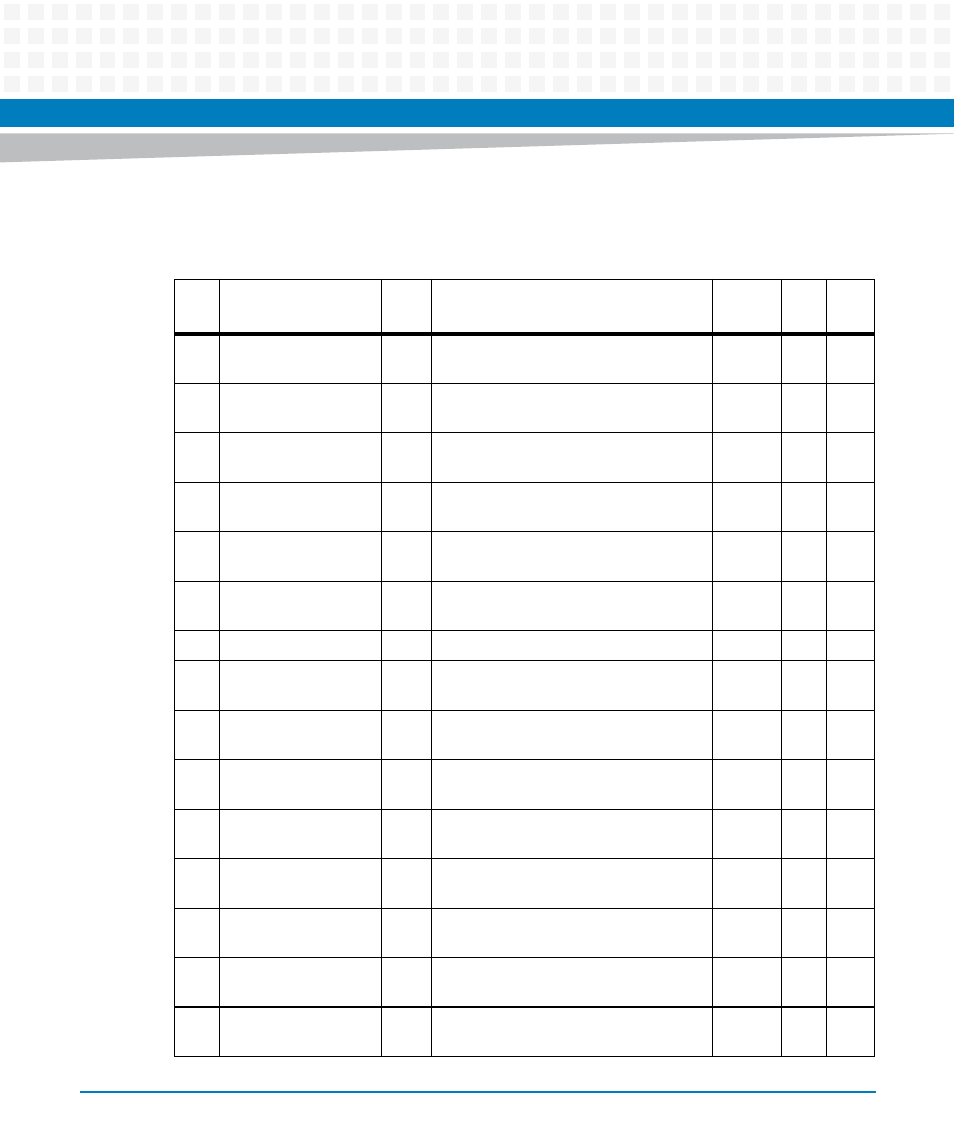

This register monitors the synchronisation and error status of different functions. If a function

signals a out of sync or an error, the respective bit is set. It can be reset by writing the respective

bit in SyncErrMonResReg.

Bit

Acronym

Type

Description

Default

Pwr

Soft

31

SerdesCltIfIntrpt3

R

0b1: SerdesCltIfIntrpt3, Interrupt from

Serdes Quad3

undef

-

-

30

SerdesCltIfIntrpt2

R

0b1: SerdesCltIfIntrpt2, Interrupt from

Serdes Quad2

undef

-

-

29

SerdesCltIfIntrpt1

R

0b1: SerdesCltIfIntrpt1, Interrupt from

Serdes Quad1

undef

-

-

28

SerdesCltIfIntrpt0

R

0b1: SerdesCltIfIntrpt0, Interrupt from

Serdes Quad0

undef

-

-

27

Spi2BusRdyTmOut

R

0b1: Spi2BusRdyTmOut, ready timed

out at Spi bus 2

undef

-

-

26

Spi1BusRdyTmOut

R

0b1: Spi1BusRdyTmOut, ready timed

out at Spi bus 1

undef

-

-

25

-

-

reserved

undef

-

-

24

LcBusRdyTmOut

R

0b1: LcBusRdyTmOut, ready timed out

at local bus

undef

-

-

23

ParErrDrpSbi1

R

0b1: ParErrDrpSbi1, parity error in SBI

drop data from Sonet/Sdh-framer1

undef

-

-

22

ParErrDrpSbi0

R

0b0: ParErrDrpSbi0, parity error in SBI

drop data from Sonet/Sdh-framer0

undef

-

-

21

SerdesRcvError2

R

0b0: SerdesRcvError2, the serdes

receiver2 reports errors

undef

-

-

20

SerdesRcvError1

R

0b0: SerdesRcvError1, the serdes

receiver1 reports errors

undef

-

-

19

SerdesRcvError0

R

0b0: SerdesRcvError0, the serdes

receiver0 reports errors

undef

-

-

18

SerdesTrmError2

R

0b0: SerdesTrmError2, the serdes

transmitter2 reports errors

undef

-

-

17

SerdesTrmError1

R

0b0: SerdesTrmError1, the serdes

transmitter1 reports errors

undef

-

-