Tsi fpga, 8 synchronisation and error monitor mask register – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 238

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

238

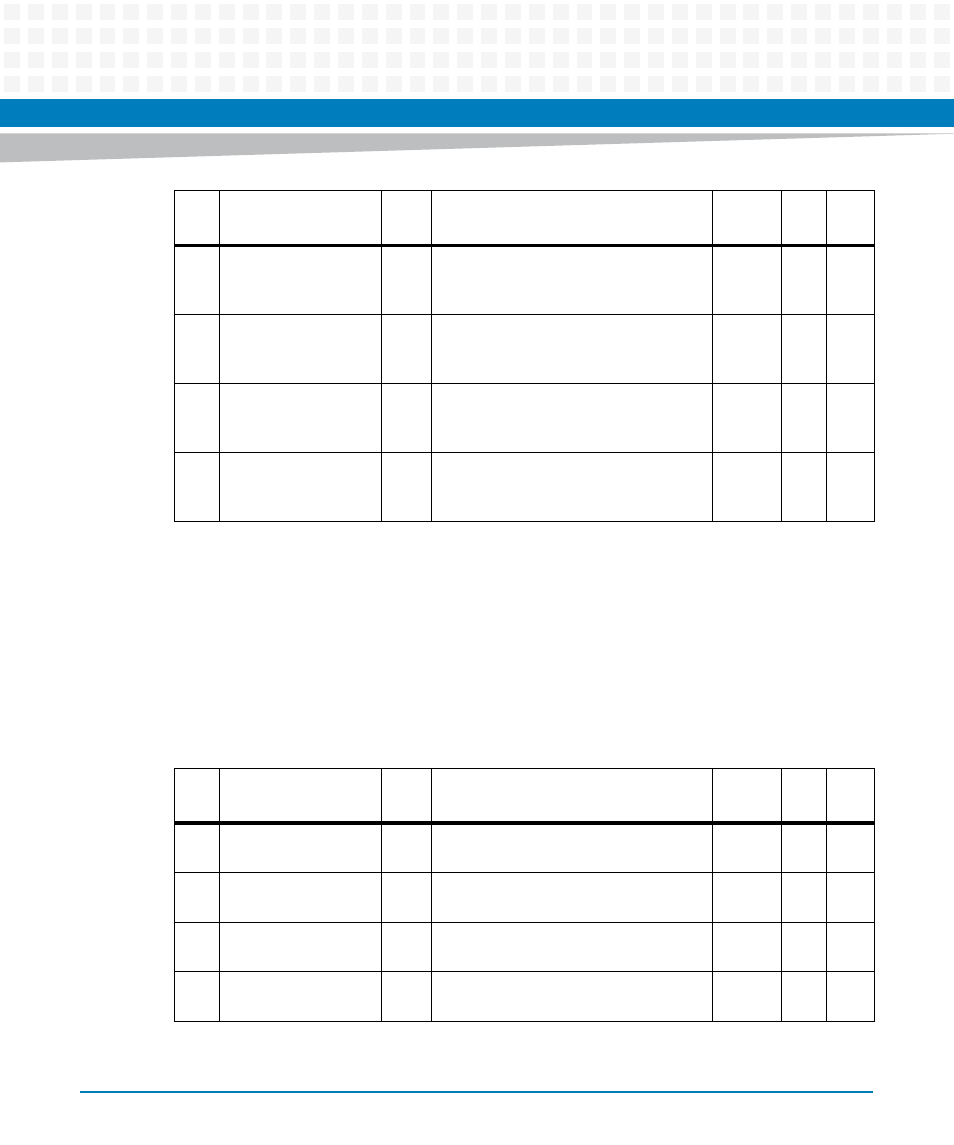

9.5.2.11.8 Synchronisation and Error Monitor Mask Register

Address:

0x1420, SyncErrMonMaskReg

Width: 32 bit

The bits of this register mask if a SyncErrInterrupt is generated when the respective bits in

SyncErrMonReg are set.

3

NoTdmEsfSyncRes

RW

0b1: NoTdmEsfSyncRes, reset no main

extended superframe 166.66Hz sync

pulse indicator

0b0

X

X

2

NoMainTdmFrameSy

ncRes

RW

0b1: NoMainTdmFrameSyncRes, reset

no main frame sync 8kHz pulse from

TDM system clock generator indicator

0b0

X

X

1

NoMainClkPllLock77

Res

RW

0b1: NoMainClkPllLock77Res, reset

main clock PLL 77.76 MHz not locked to

TDM system clock indicator

0b0

X

X

0

NoMainClkPllLock13

1Res

RW

0b1: NoMainClkPllLock131Res, reset

main clock PLL 131.072MHz not locked

to TDM system clock indicator

0b0

X

X

Bit

Acronym

Type

Description

Default

Pwr

Soft

Bit

Acronym

Type

Description

Default

Pwr

Soft

31

SerdesCltIfIntrptMas

k3

RW

0b1: SerdesCltIfIntrptEnable3, enables

Interrupt from Serdes Quad3 indicator

0b0

X

X

30

SerdesCltIfIntrptMas

k2

RW

0b1: SerdesCltIfIntrptEnable2, enables

Interrupt from Serdes Quad2 indicator

0b0

X

X

29

SerdesCltIfIntrptMas

k1

RW

0b1: SerdesCltIfIntrptEnable1, enables

Interrupt from Serdes Quad1 indicator

0b0

X

X

28

SerdesCltIfIntrptMas

k0

RW

0b1: SerdesCltIfIntrptEnable0, enables

Interrupt from Serdes Quad0 indicator

0b0

X

X