27 artm ethernet reset control register, 4 reset structure, Table 8-62 – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 151: Artm telecom clock monitor upper limit register, Table 8-63, Artm ethernet reset control register, Base artm fpga

Base ARTM FPGA

ARTM-831X Installation and Use (6806800M76E)

151

8.3.1.27 ARTM Ethernet Reset Control Register

8.4

Reset Structure

There is one asynchronous reset domain SPP_RTM_RST_ on FPGA. The reset signal

SPP_RTM_RST_ resets all internal registers to their default values

After FPGA configuration is done all internal registers are set to their default values, which is the

same behavior as SPP_RTM_RST_ is deasserted.

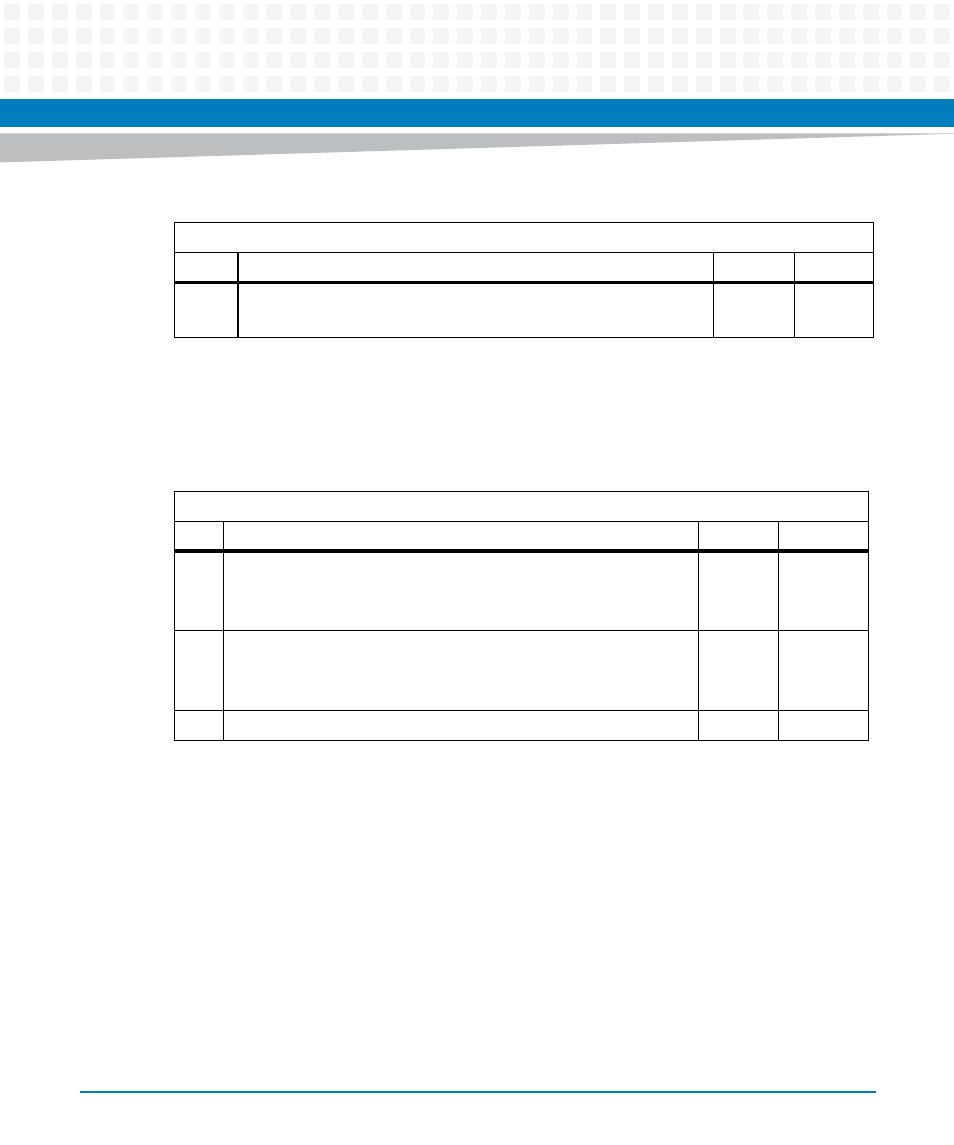

Table 8-62 ARTM Telecom Clock Monitor Upper Limit Register

Address: 0x2A- 0x2B

Bit

Description

Default

Access

15:0

Upper Limit for supervised Telecom Clock:

Used by Telecom Clock Monitor Out of Range Register.

0

RTM: r/w

Table 8-63 ARTM Ethernet Reset Control Register

Address: 0x30

Bit

Description

Default

Access

0

ARTM GE Ethernet Reset Control (signal N54640_RST_):

0: Reset signal N54640_RST_ is only controlled by ETH_RST_

1: Reset signal N54640_RST_ is driven low

0

RTM: r/w

MMC: r/w

1

ARTM 10GE Ethernet Reset Control (signal N8707_RST_):

0: Reset signal N8707_RST_ is only controlled by ETH_RST_

1: Reset signal N8707_RST_ is driven low

0

RTM: r/w

MMC: r/w

7:2

Reserved

0

r