Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 186

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

186

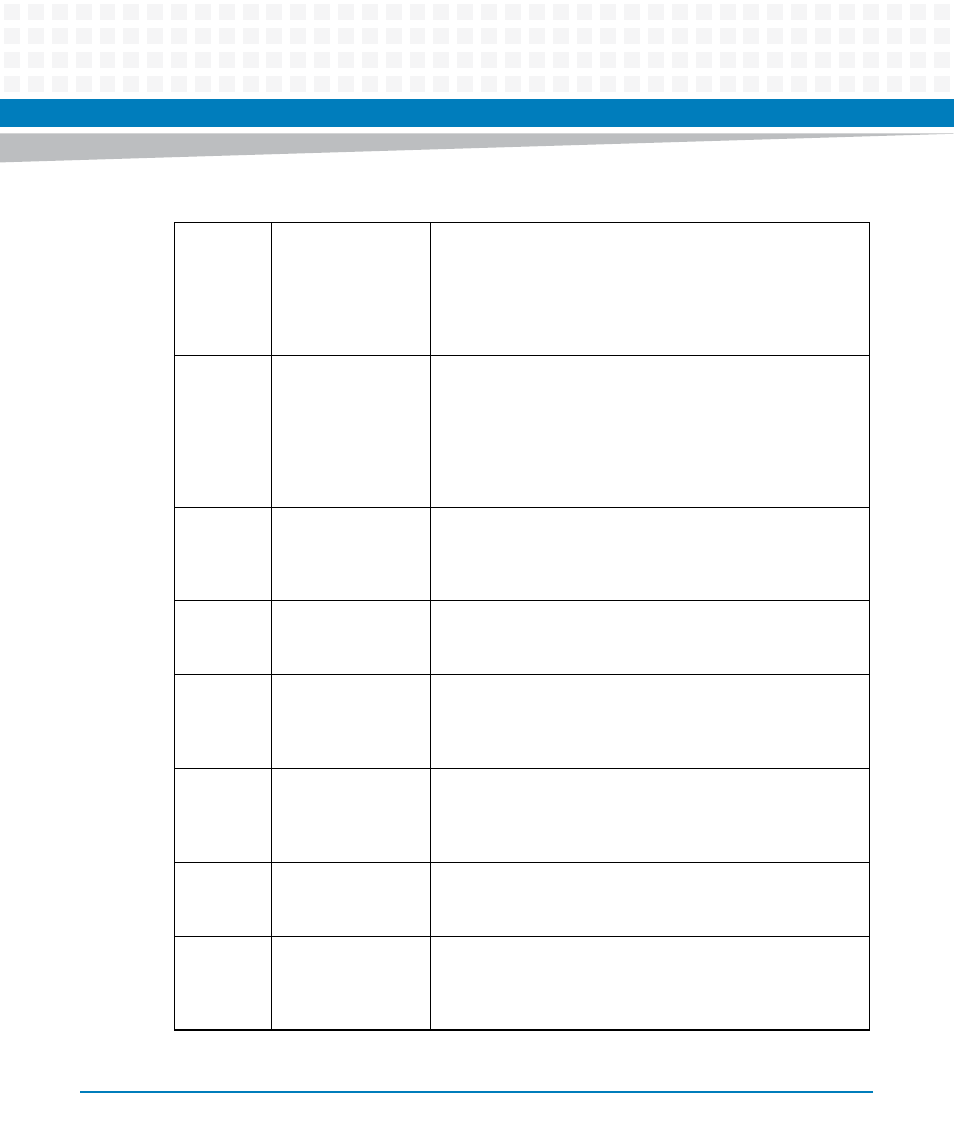

0x1474

CompEvtReg

Component Event Status Register (32bit) [Hw: syn, WAck1,

RAck1]

This register monitors the internal and external components,

eg. Xrt86 framer, interrupt status. If an interrupt occurs, the

respective bit is set. It can be reset by writing the respective bit

in ExtCompEvtReg.

0x1478

CompEvtResReg

Component Event Status Reset Register (32bit) [Hw: syn,

WAck1, RAck1]

The bits of this register reset the respective bits in

CompEvtReg. Writing a 1 to a bit in CompEvtResReg resets the

corresponding bit in CompEvtReg The interrupt bit in

CompEvtReg is kept reset until writing a 0 to the corresponding

bit in CompEvtResReg re-enables its monitor function again.

0x147C

CompEvtMaskReg

Component Event Status Mask Register (32bit) [Hw: syn,

WAck1, RAck1]

The bits of this register mask the bits of the CompEvtReg for the

generation of a Interrupt (MSI) to the host via PCIE.

0x1480

UnOccpdAddrMonR

eg

Unoccupied Address Access Monitor Register (8bit) [Hw: syn,

WAck1, RAck1]

This register monitors the access to unoccupied address areas

0x1481

UnOccpdAddrMonR

esetReg

Unoccupied Address Access Monitor Reset Register (8bit) [Hw:

syn, WAck1, RAck1]

This register resets the access to unoccupied address area

monitor and unoccupied address area address registers

0x1484

UnOccpdAddrMonA

ddrReg

Unoccupied Address Access Monitor Address Register (32bit)

[Hw: syn, WAck1, RAck1]

This register stores the address of the last access to an

unoccupied address area

0x1490

LclBusMonReg

Local Bus Access Monitor Register (8bit) [Hw: syn, WAck1,

RAck1]

This register monitors the access to the local bus

0x1491

LclBusMonResetReg

Local Bus Access Monitor Reset Register (8bit) [Hw: syn, WAck1

, RAck1]

This register resets the timeout flag in the respective monitor

and address registers

Table 9-5 RTM FPGA Address map Overview (continued)