Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 248

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

248

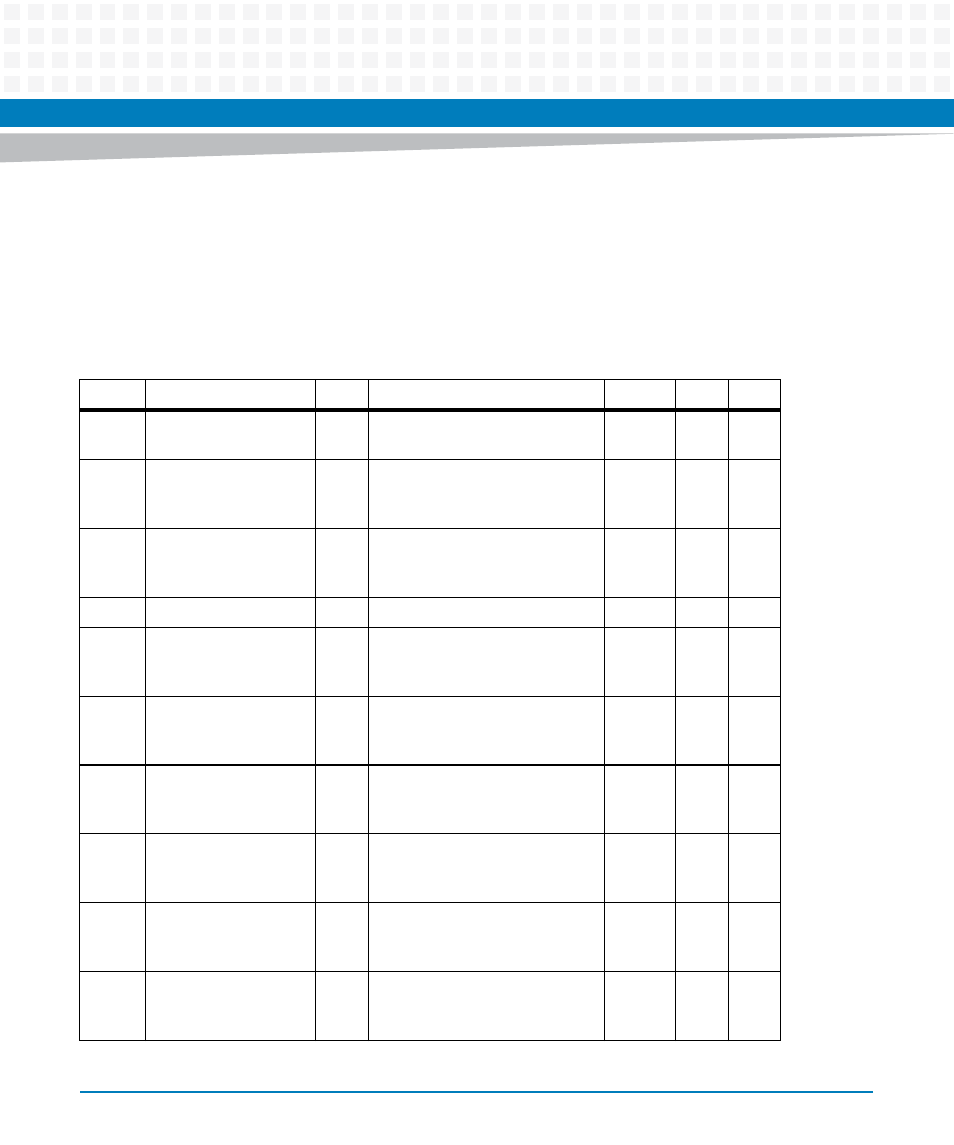

0x1478, CompEvtResReg

Width: 32 bit

The bits of this register reset the respective bits in CompEvtReg. Writing a 1 to a bit in

CompEvtResReg resets the corresponding bit in CompEvtReg The interrupt bit in CompEvtReg

is kept reset until writing a 0 to the corresponding bit in CompEvtResReg re-enables its monitor

function.again.

Bit

Acronym

Type

Description

Default

Pwr

Soft

31

Gr8IntrptReset

RW

0b1: Gr8IntrptReset, resets

CompEvtReg bitGr8Intrpt

0b0

X

X

30

Spi2IntrptReset

RW

0b1: Spi2IntrptReset, resets the

Spi bus 2 (from BaseExtFpga)

interrupt indicator

0b0

X

X

29

Spi1IntrptReset

RW

0b1: Spi1IntrptReset, resets the

Spi bus 1 (from ExtFpga)

interrupt indicator

0b0

X

X

28...12 -

-

reserved

undef

-

-

11

Xrt75ChpIntrptReset3 RW

0b1: Xrt75ChpIntrptReset3,

resets CompEvtReg bit

IntrptXrt75_3

0b0

X

X

10

Xrt75ChpIntrptReset2 RW

0b1: Xrt75ChpIntrptReset2,

resets CompEvtReg bit

IntrptXrt75_2

0b0

X

X

9

Xrt75ChpIntrptReset1 RW

0b1: Xrt75ChpIntrptReset1,

resets CompEvtReg bit

IntrptXrt75_1

0b0

X

X

8

Xrt75ChpIntrptReset0 RW

0b1: Xrt75ChpIntrptReset0,

resets CompEvtReg bit

IntrptXrt75_0

0b0

X

X

7

Xrt86ChpIntrptReset5 RW

0b1: Xrt86ChpIntrptReset5,

resets CompEvtReg bit

IntrptXrt86_5

0b0

X

X

6

Xrt86ChpIntrptReset4 RW

0b1: Xrt86ChpIntrptReset4,

resets CompEvtReg bit

IntrptXrt86_4

0b0

X

X