Tsi fpga, 12lvds partner mfs offset register, 13component reset register – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 244

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

244

The bits of this register show if a valid partner multi-frame-sync pulse is received via the path

overhead interface of sonet/sdh framer 0. Further the offset the received partner multi-frame-

sync pulse to the own framesync pulse is shown. The offset can be 0 to 47 frames (125us),

measured as distance behind the own pulse. The received partner frampulse is judged as valid,

if 2 pulses occur one time in the expected distance, measured with the own 131.072 MHz

clock.

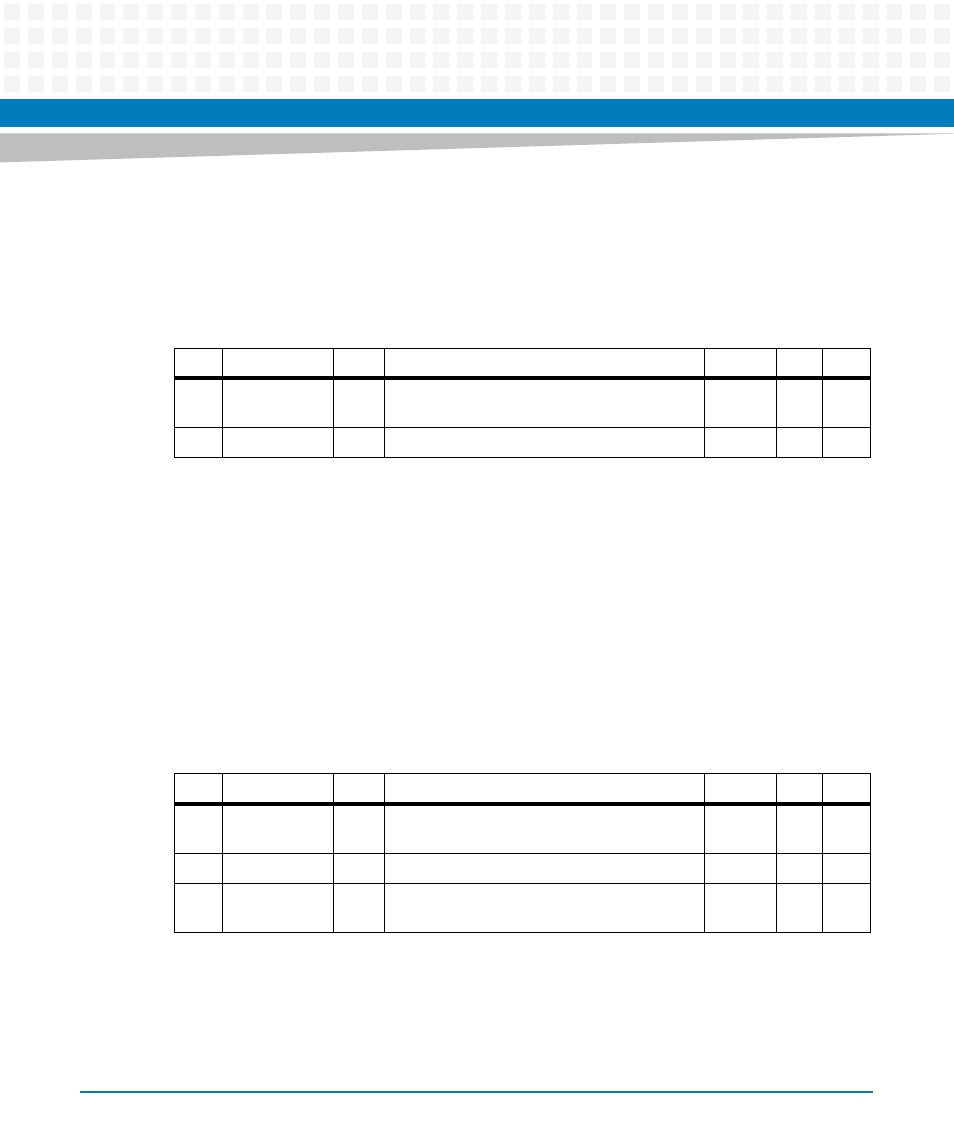

9.5.2.11.12Lvds Partner Mfs Offset register

Address:

0x1461, LvdsPartnerMfsOffsetReg

Width: 8 bit

The bits of this register show if a valid partner multi-frame-sync pulse is received via lvds link.

Further the offset the received partner multi-frame-sync pulse to the own framesync pulse is

shown. The offset can be 0 to 47 frames (125us), measured as distance behind the own pulse.

The received partner frampulse is judged as valid, if 2 pulses occur one time in the expected

distance, measured with the own 131.072 MHz clock.

9.5.2.11.13Component Reset Register

Address:

0x1470, CompResReg

Bit

Acronym

Type Description

Default

Pwr

Soft

7

PrtnPohMfsVl

d

R

0b1: PrtnPohMfsVld, A valid partner Poh Mfs

is received

0b0

F

F

6

-

-

reserved

undef

-

-

Bit

Acronym

Type Description

Default

Pwr

Soft

7

PrtnLvdsMfsV

ld

R

0b1: PrtnLvdsMfsVld, A valid partner Lvds Mfs

is received

0b0

F

F

6

-

-

reserved

undef

-

-

5...

0

LvdsMfsOffSe

t

R

Partner Lvds Mfs behind own Mfs offset in

multiples of 125us (0...47)

undef

-

-