Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 176

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

176

0x1010

TsiChnCntReg

Tsi Channel Counter Register (32bit) [Hw: asyn, WAck4, RAck4]

The TsiChnCntReg shows the currently processed channels by

the Tsi and increments in steps of 4, since 4 channels are always

processed during the same period of time. There is no action

with the Tsi where this register has to be considered.

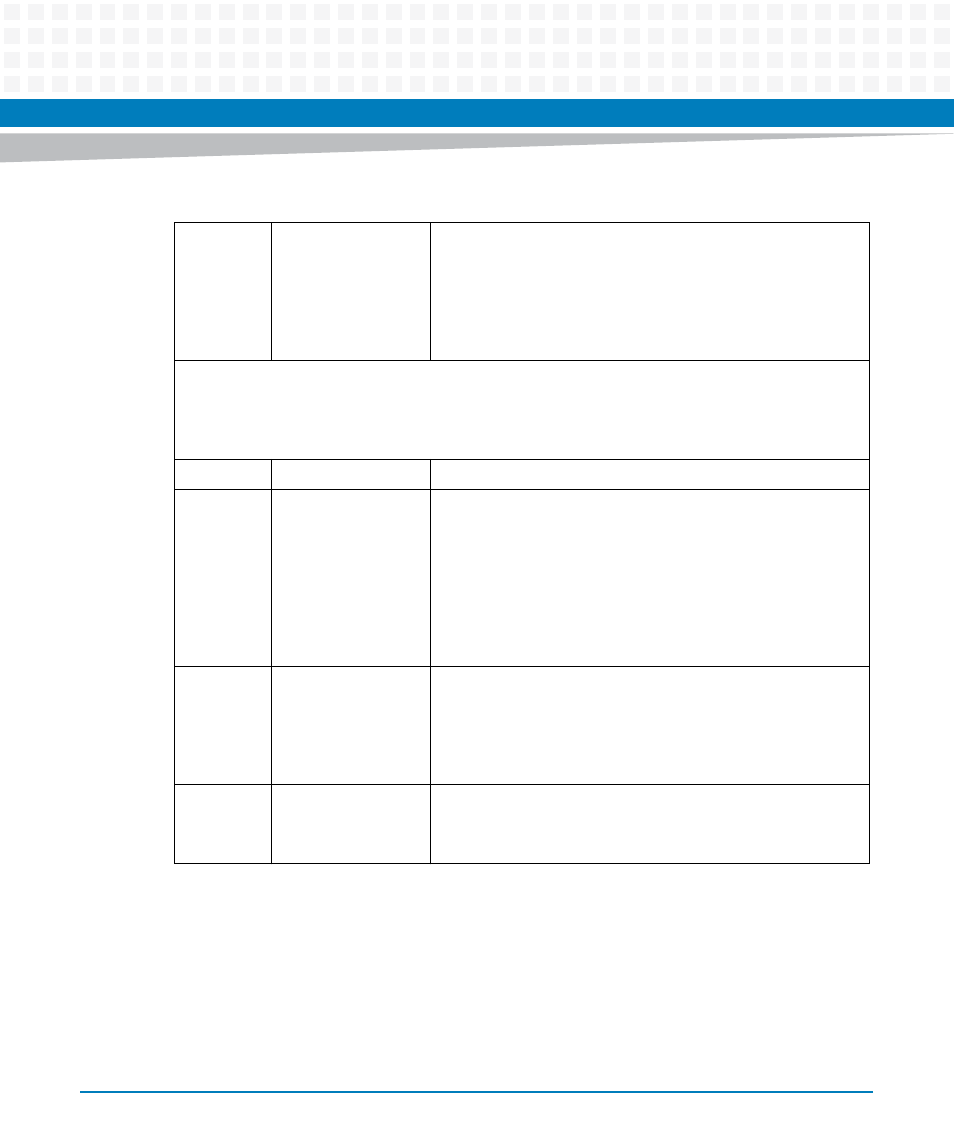

Gr8 Registers (Gr8Regs) [Hw: Cy1, InR, OutR]

Gr8 Control and Status Register

Access via PCI-bus 512kByte non-prefetchable memory area of 64bit-bar[3,2], hereof assigned to this

block: 1040...107F

Address

Acronym

Description

0x1040

Gr8InitReg

Gr8 Initialization Register (32bit) [Hw: asyn, WAck4, RAck4,

WRP]

The Gr8TrmMem cells are written with 0x0000 from

TsiInitValReg during the first 27ms after power-on reset, thus

disabling all output channels. A reinitialisation in the same

manner can be started later again by Gr8InitReg. The

initialization process can be monitored with Gr8InitMonReg.

0x1044

Gr8InitMonReg

Gr8 Initialization Monitor Register (32bit) [Hw: asyn, WAck4,

RAck4]

The Gr8TrmMem initialization and can be monitored (takes 18-

27ms).

0x1048

Gr8CtrlReg

Gr8 Control Register (32bit) [Hw: asyn, WAck4, RAck4]

Enables Gr8 transmitter or receiver

Table 9-5 RTM FPGA Address map Overview (continued)