Table 9-20, Tsi channel map for dsp 0 (serdes) block, Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 289

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

289

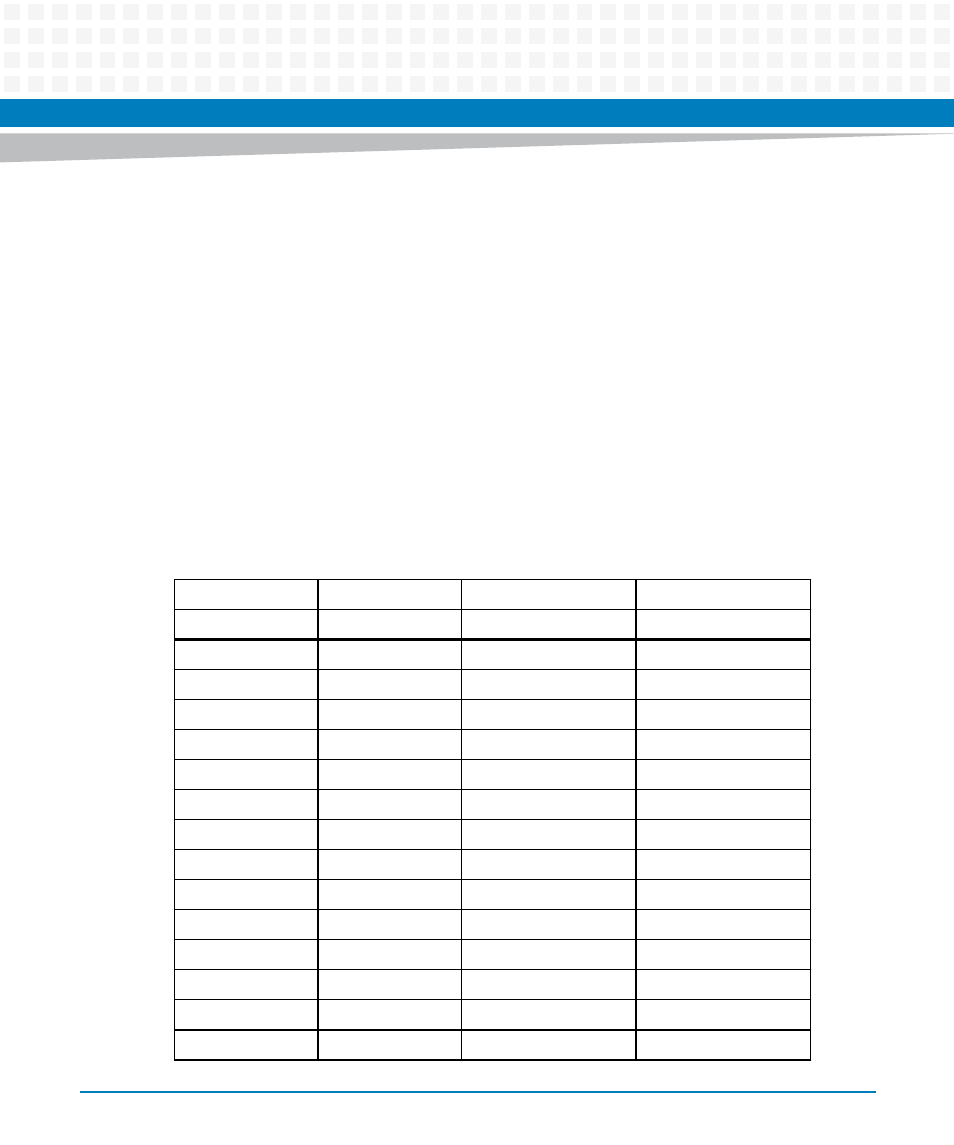

The table describes the lower 10 bits of the 65.536 channels of the channel address of the TSI.

Depending on the combination of the lower fixed address bits the channels are assigned to the

peripheral interfaces. The bits with the value '0' or '1' in the table assign a unique slice of

channels for the peripheral interface. The upper bits (10 to 15) of the TSI channel counter and

a number of lower bits marked with 'x' number the sequence of the peripheral interface

channel. The more of these 'x' bits, the larger is the amount of channels for the slice (1x64= 64

up to 128x64= 8192).

For example, the slice of HMVIP 0 has 8 bits defined to (0b00010000) and the rest of the 16 bit

TSI addresses are not fixed. That means, that the HMVIP 0 peripheral interface starts with the

TSI channel 0x0010 (16) and the next channel is after 28 = 256 channels and so on (0x0110,

0x0210, … , 0xFF10). The total number of channels for this interface is 256.

For other interfaces like DSP 0 more than one slice has to be considered. In this case the channel

count of the interface resulted by interleaving the slices as shown in the following table.

Table 9-20 TSI channel map for DSP 0 (SerDes) block

DSP 0

TSI

cycle

cycle

channel sequence

channel sequence

slice of 128x64 channel slice of 32x64 channel

0x0000

0x0001

Start (128)

-

0x0001

0x0004

-

Start (32)

0x0002

0x0009

+8

-

0x0003

0x0011

+8

-

0x0004

0x0019

+8

-

0x0005

0x0021

+8

-

0x0006

0x0024

-

+32

0x0007

0x0029

+8

-

:

:

:

:

0x009E

0x03F1

+8

-

0x009F

0x03F9

+8

-

0x00A0

0x0401

+8

-

0x00A1

0x0404

-

+32

:

:

:

: