Tsi fpga – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 200

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

200

The cells 772,773, ... 775 match to the T1 interface 0 (Xrt86 framer chip 0) channel 4,5,6,7,

...

The cells 816,817 ... 1023 unused

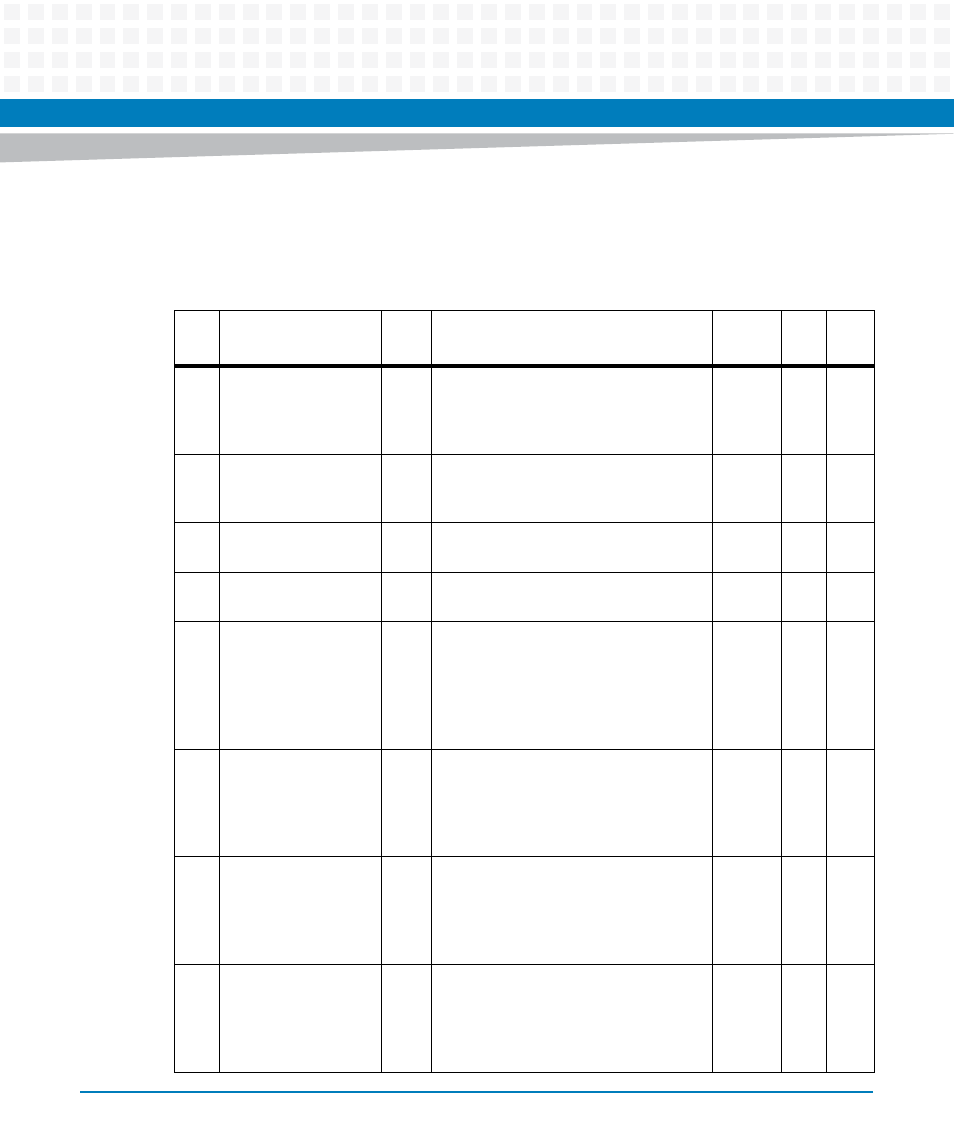

Bit

Acronym

Type

Description

Default

Pwr

Soft

31

Gr8RcvEn

R

0b1: Gr8RcvEnabled, The receiver of

the channel is enabled (automatically

set when the respective transmitter is

enabled).

undef

-

-

30

Gr8RcvMessageValid

R

0b1: Gr8RcvMessageValid, There is no

valid data link message represented in

the other bits of this register

undef

-

-

29..

.27

Gr8RcvLatestBits

R

These bits represent the latest 3 bits

received in this channel (FS and FT).

undef

-

-

26..

.20

Gr8RcvCtrlCount

R

Shows progress in recognizing a valid

datalink message

undef

-

-

19..

.16

Gr8RcvPrtSwFld

R

These bits contain the bits received in

the protection switch field of the

previous incoming data link message

for the associated channel. S1

corresponds to bit 16, S4 corresponds

to bit 19

undef

-

-

15..

.14

Gr8RcvAlrmFld

R

These bits contain the bits received in

the alarm field of the previous

incoming data link message for the

associated channel. A1 corresponds to

bit 14, A2 corresponds to bit 15

undef

-

-

13..

.11

Gr8RcvMaintFld

R

These bits contain the bits received in

the maintenance field of the previous

incoming data link message for the

associated channel. M1 corresponds to

bit 11, M3 corresponds to bit 13

undef

-

-

10..

.0

Gr8RcvCncntrFld

R

These bits contain the value received in

the concentrator field of the previous

incoming data link message for the

associated channel. C1 corresponds to

bit 0, C11 corresponds to bit 10

undef

-

-