9 local bus master interface, Table 9-3, Local bus interface signals – Artesyn ARTM-831X Installation and Use (June 2014) User Manual

Page 168: Tsi fpga

TSI FPGA

ARTM-831X Installation and Use (6806800M76E)

168

The resource decoder is an implementation specific block that maps address regions in the PCI

BARs to resources on the wishbone interface. Each BAR can either map to a single wishbone

resource or can be subdivided to a number of wishbone resources. The logic in this block must

be purely combinational and since it is accessed during the decode stage of the state machine

in the Wishbone Master Adapter.

The wishbone master adapter accepts and decodes all incoming packets from the Lattice

PCIexpress core. Posted and non-posted requests are converted to wishbone access cycles. In

the case of non-posted read requests, the data returned from the wishbone access sequence

is used as the payload in the PCIexpress completion packet returned to the requester.

9.4.9

Local Bus Master Interface

The Local Bus Interface is an asynchronous, parallel, none multiplexed, memory mapped

interface for I/O read and write operations according to Intel bus mode. The data bus width is

16 bit. The address bus width is 17 bit. The access to 16 bit devices (e.g. PM8310) is always

word aligned. DMA is not supported on local bus.

There are four to eight peripheral devices connected to the Local Bus Interface pins dependent

on the RTM variant.

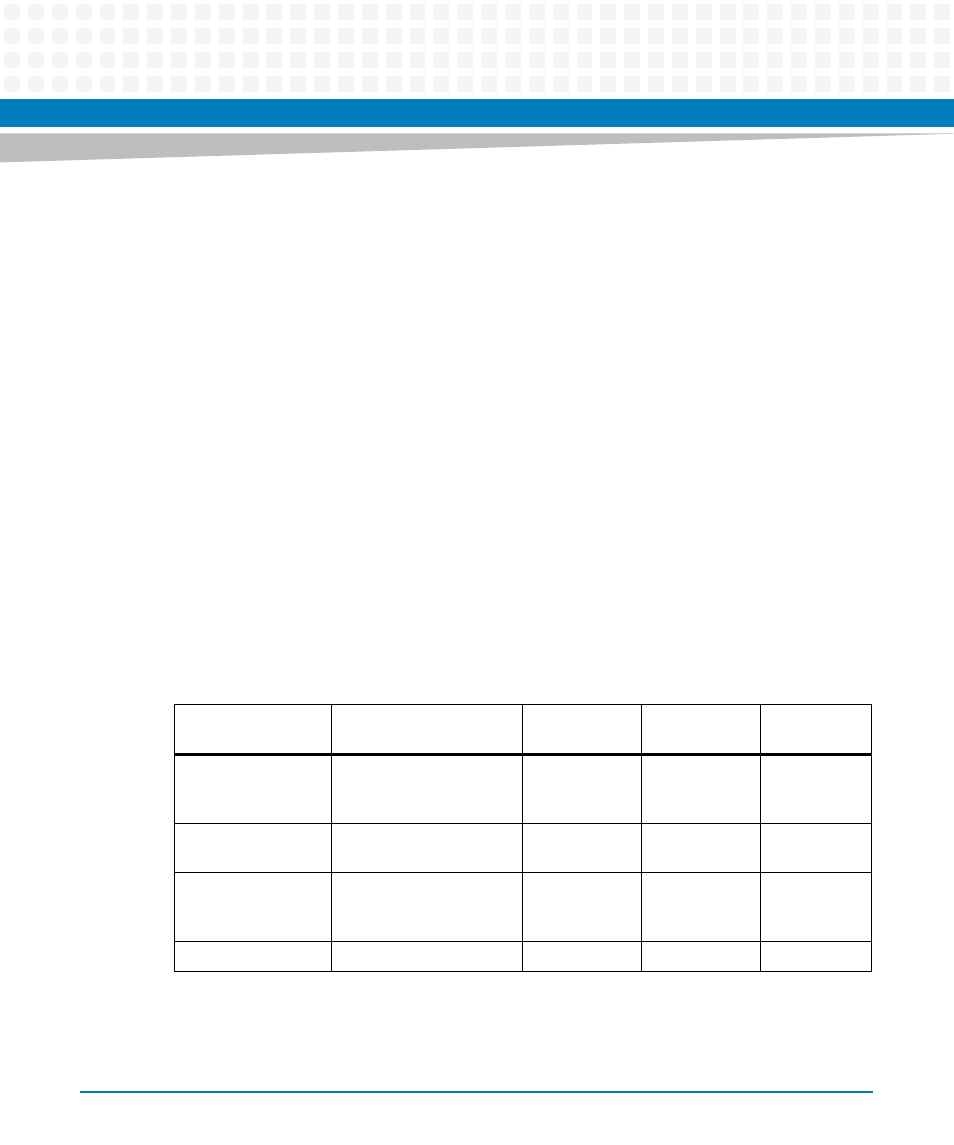

Table 9-3 Local bus interface signals

Asynchronous Parallel

Interface Signals

Variant 1: 48 x

E1/T1

Variant 2: 8x

OC-3

Variant 3: 24

x DS3

Exar XRT86VX38

ALE, CS_L, RD_L. WR_L,

ADR(14..0), DAT(7..0),

RDY_L

6x

2x

2x

PMC Sierra PM8310

ALE, CS_L, RD_L, WR_L,

ADR(15..0); DAT(15..0)

--

2x

2x

Exar XRT75R06D

CS_L, RD_L, WR_L,

ADR(7..0), DAT(7..0),

RDY_L

--

--

4x

Total

6 Devices

4 Devices

8 Devices