Appendixa register summary, Tablea.1 lsi53c1010r pci register map, Appendix a, register summary – Avago Technologies LSI53C1010R User Manual

Page 365: Appendix a, Register summary, Lsi53c1010r pci register map, Appendix a register summary

LSI53C1010R PCI to Dual Channel Ultra160 SCSI Multifunction Controller

A-1

Version 2.2

Copyright © 2000–2003 by LSI Logic Corporation. All rights reserved.

Appendix A

Register Summary

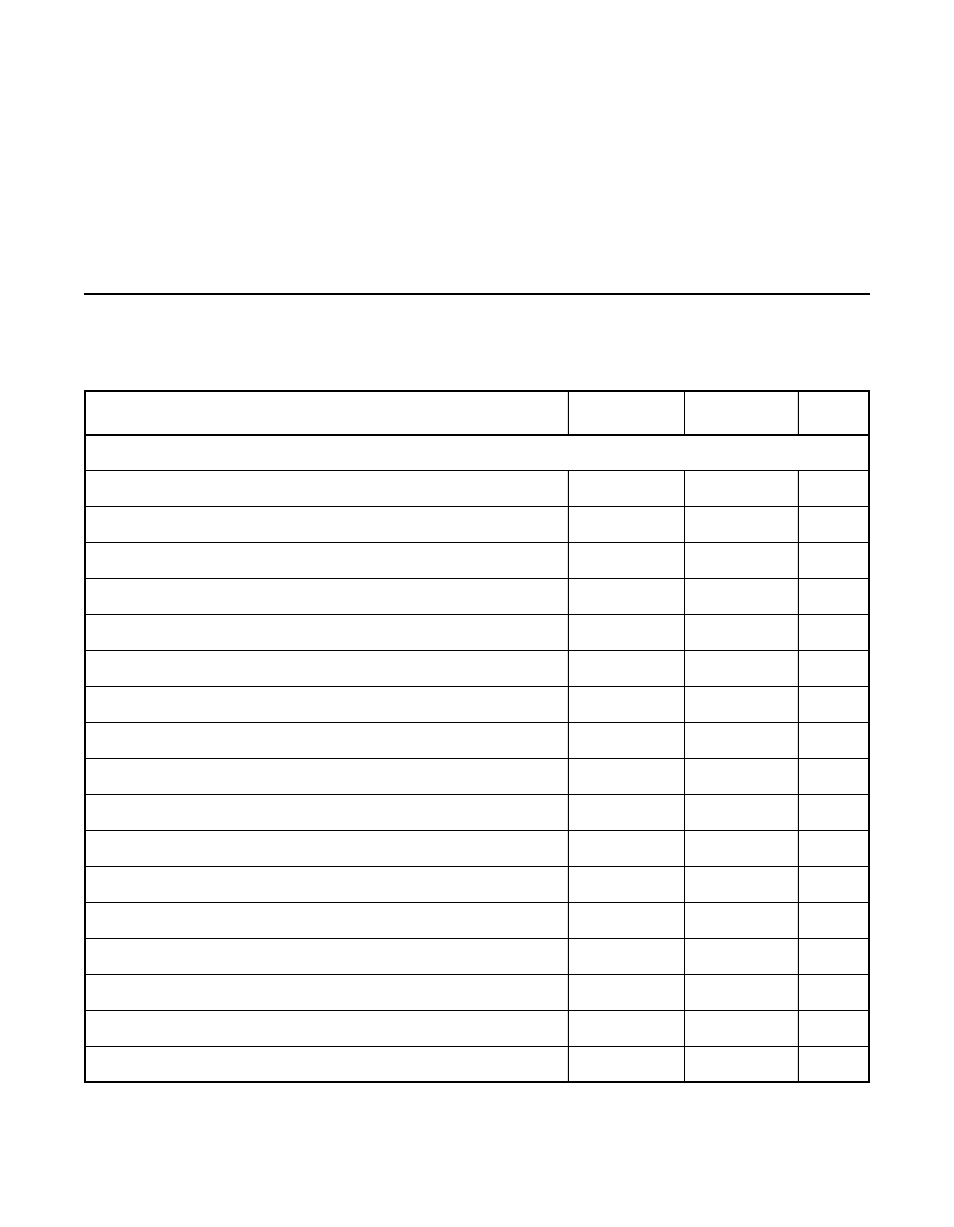

lists the LSI53C1010R PCI registers by register name.

Table A.1

LSI53C1010R PCI Register Map

Register Name

Address

Read/Write

Page

PCI Registers

Base Address Register Four (BAR4) (SCRIPTS RAM)

Base Address Register One (BAR1) (MEMORY)

Base Address Register Three (BAR3) (SCRIPTS RAM)

Base Address Register Two (BAR2) (MEMORY)

Base Address Register Zero (BAR0) (I/O)

Bridge Support Extensions (PMCSR_BSE)