Spi timing – Digi NS9750 User Manual

Page 851

w w w . d i g i e m b e d d e d . c o m

8 2 7

T i m i n g

SPI timing

Note:

All AC characteristics are measured with 10pF, unless otherwise noted.

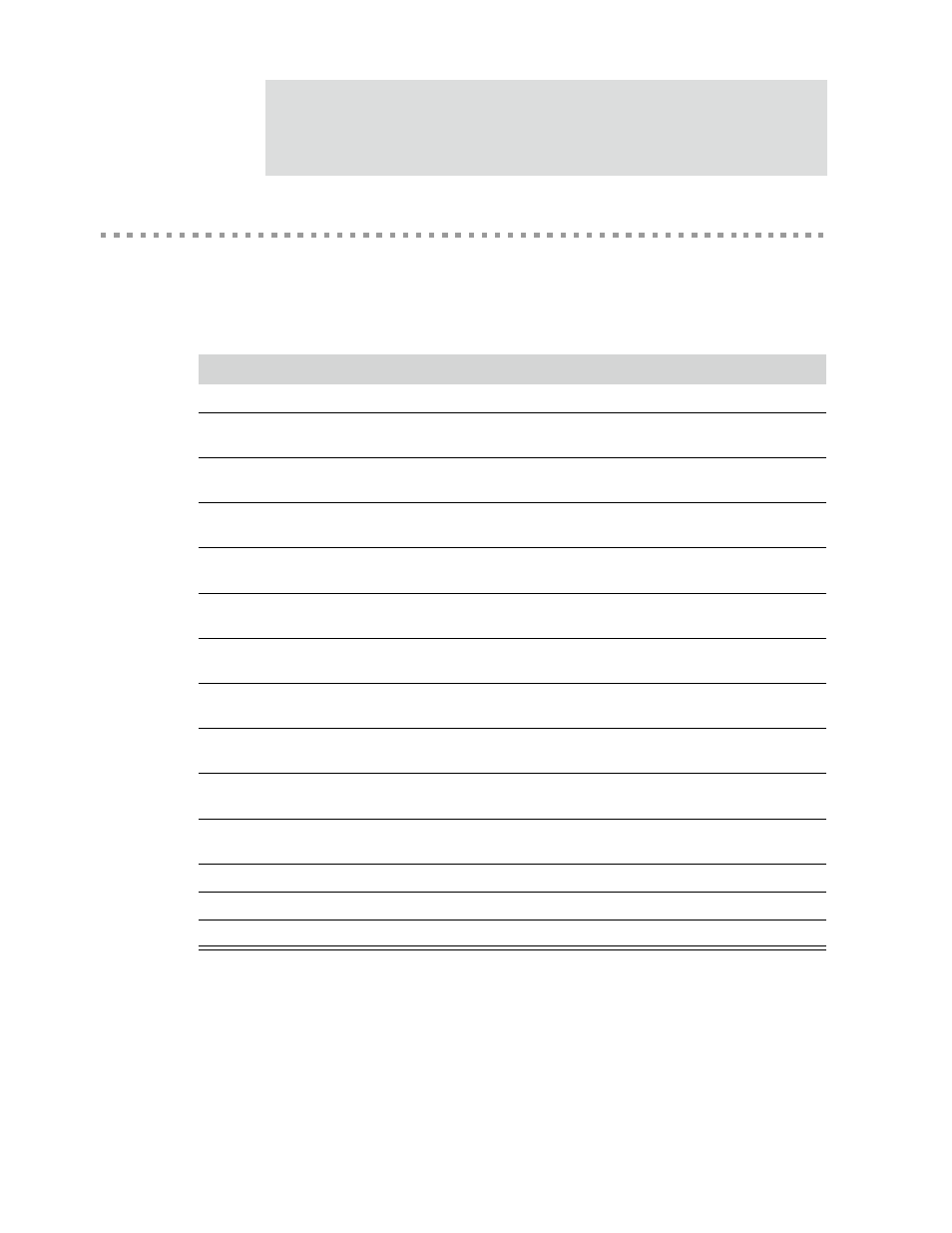

Table 475 describes the values shown in the SPI timing diagrams (Figure 136 through

Figure 139).

Parm

Description

Min

Max

Units

Modes

Notes

SPI master parameters

SP0

SPI enable low setup to first SPI

CLK out rising

3*T

BCLK

-10

ns

0, 3

1, 3

SP1

SPI enable low setup to first SPI

CLK out falling

3*T

BCLK

-10

ns

1, 2

1, 3

SP3

SPI data in setup to SPI CLK out

rising

30

ns

0, 3

SP4

SPI data in hold from SPI CLK out

rising

0

ns

0, 3

SP5

SPI data in setup to SPI CLK out

falling

30

ns

1, 2

SP6

SPI data in hold from SPI CLK out

falling

0

ns

1, 2

SP7

SPI CLK out falling to SPI data out

valid

10

ns

0, 3

6

SP8

SPI CLK out rising to SPI data out

valid

10

ns

1, 2

6

SP9

SPI enable low hold from last SPI

CLK out falling

3*T

BCLK

-10

ns

0, 3

1, 3

SP10

SPI enable low hold from last SPI

CLK out rising

3*T

BCLK

-10

ns

1, 2

1, 3

SP11

SPI CLK out high time

SP13*45%

SPI3*55%

ns

0, 1, 2, 3

4

SP12

SPI CLK out low time

SP13*45%

SPI3*55%

ns

0, 1, 2, 3

4

SP13

SPI CLK out period

T

BCLK

*6

ns

0, 1, 2, 3

3

SPI slave parameters

Table 475: SPI timing parameters