Digi NS9750 User Manual

Page 758

U S B h o s t b l o c k r e g i s t e r s

7 3 4

N S 9 7 5 0 H a r d w a r e R e f e r e n c e

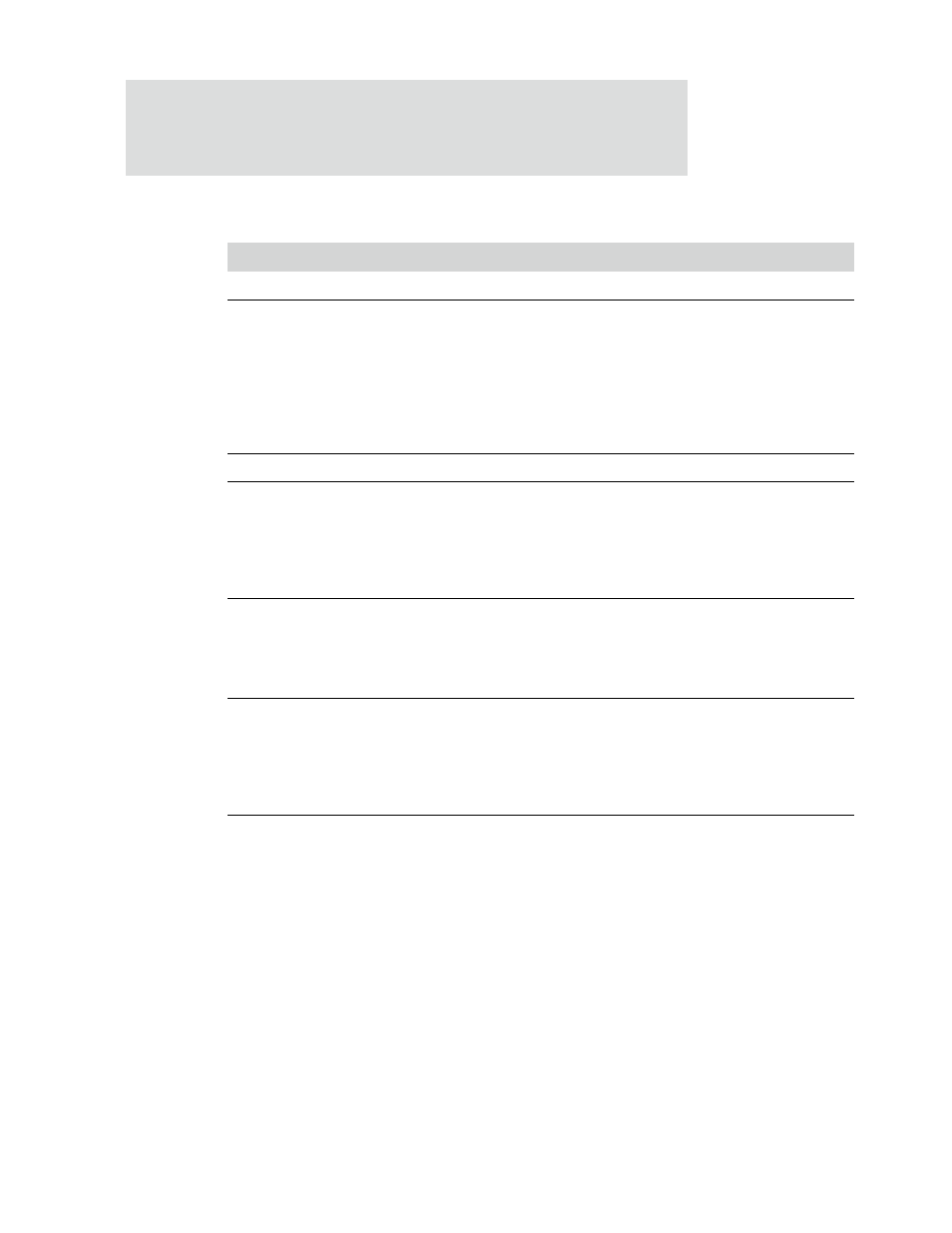

Register bit assignment

Bits

Access

Mnemonic

Reset

Description

D31

N/A

Reserved

N/A

N/A

D30

R/W

OC

0b

OwnershipChange

Set by the host controller when the host controller driver

sets the OwnershipChangeRequest field in the

HcCommandStatus register (see "HcCommandStatus

register," beginning on page 730). This event, when

unmasked, always generates a system management

interrupt (SMI) immediately.

This bit is tied to 0b when the SMI pin is not implemented.

D29:07

N/A

Reserved

N/A

N/A

D06

R/W

RHSC

0b

RootHubStatusChange

Set when the content of the HcRhStatus register (see

"HcRhStatus register," beginning on page 756) or any

HcRhPortStatus[NumberofDownstreamPort] register (see

"HcRhPortStatus[1] register," beginning on page 759) has

changed.

D05

R/W

FNO

0b

FrameNumberOverflow

Set when the most significant bit (MSB), bit 15, of the

HcFmNumber (see "HcFmNumber register," beginning

on page 749) changes value, from 0 to 1 or 1 to 0, and after

HccaFrameNumber has been updated.

D04

R/W

UE

0b

UnrecoverableError

Set when the host controller finds a system error not

related to USB. The host controller should not proceed

with any processing nor signaling before the system error

has been corrected. The host controller driver clears this

bit after the host controller has been reset.

D03

R/W

RD

0b

ResumeDetected

Set when the host controller finds that a device on the USB

is asserting resume signaling. The transition from no

resume signaling to resume signaling causes this bit to be

set.

This bit is not set when the host controller driver sets the

USBRESUME

state.

Table 426: HcInterruptStatus register