Digi NS9750 User Manual

Page 420

E t h e r n e t C o n t r o l a n d S t a t u s r e g i s t e r s

3 9 6

N S 9 7 5 0 H a r d w a r e R e f e r e n c e

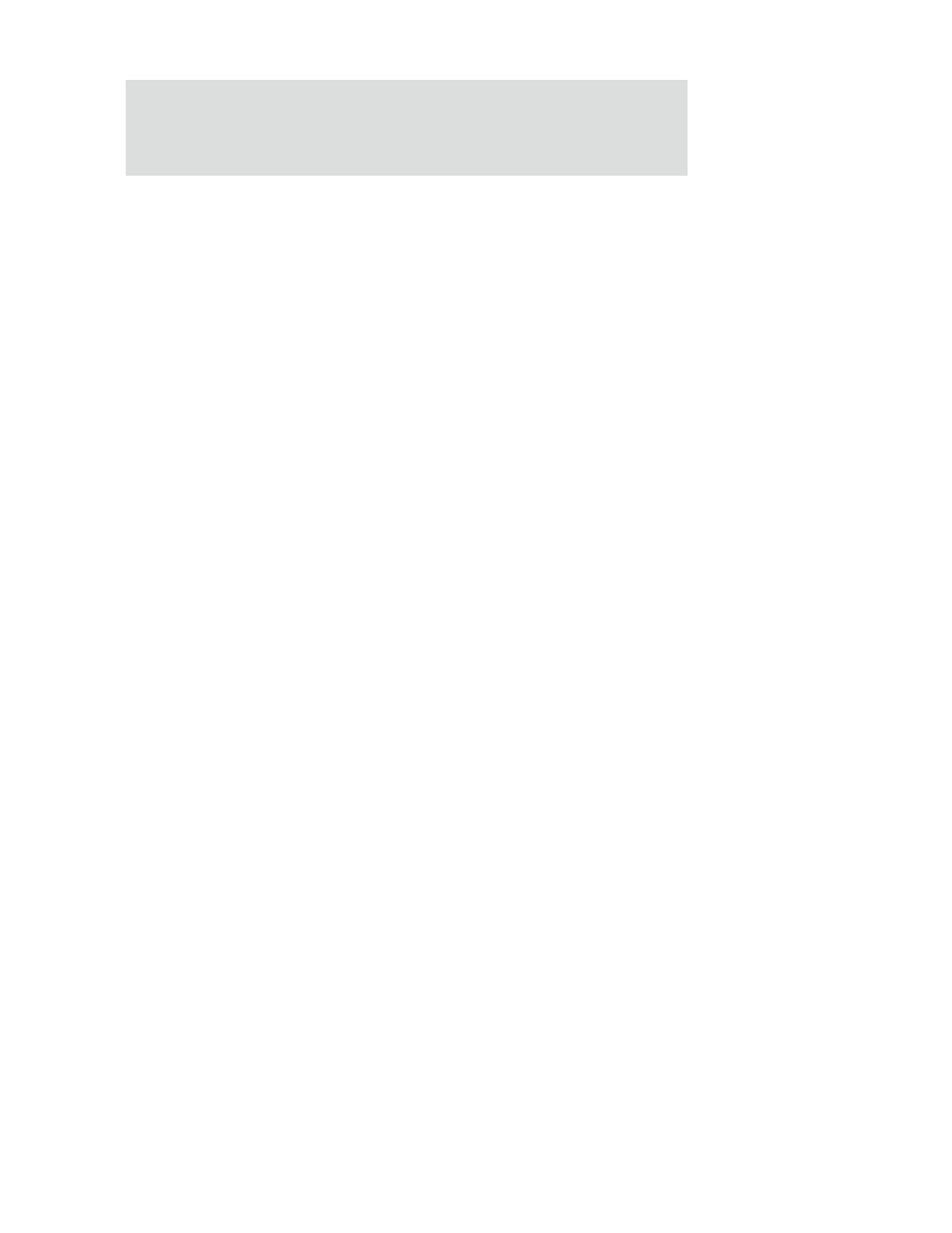

TX buffer descriptor RAM

Address: A060 1000

The TX buffer descriptor RAM holds 64 transmit buffer descriptors on-chip. Each

buffer descriptor occupies four locations in the RAM, and the RAM is implemented as

a 256x32 device. This is the format of the TX buffer descriptor RAM:

Offset+0

Offset+4

Offset+8

Offset+C

See Figure 67, "Transmit buffer descriptor format," on page 327, for more information

about the fields in Offset+C.

D31:00

R/W

Source address

D31:11

R/W

Not used

D10:00

R/W

Buffer length

D31:00

R/W

Destination address (not used)

D31

R/W

W

Wrap

D30

R/W

I

Interrupt on buffer completion

D29

R/W

L

Last buffer on transmit frame

D28

R/W

F

Buffer full

D27:16

R/W

Reserved

N/A

D15:00

R/W

Status

Transmit status from MAC