Interrupt status and control register, Table 392: interrupt status and control register – Digi NS9750 User Manual

Page 705

w w w . d i g i e m b e d d e d . c o m

6 8 1

I E E E 1 2 8 4 P e r i p h e r a l C o n t r o l l e r

Interrupt Status and Control register

Address: 9040 0004

The Interrupt Status and Control register contains miscellaneous control settings for

the IEEE 1284 module. Bits with an access type of R/C (read/clear) can be set only by

hardware, and are cleared by software by writing a 1 to the corresponding bit

location. The software is expected to clear the condition causing the interrupt before

clearing the interrupt; if the condition is not cleared, the bit and (maskable)

interrupt will be reasserted.

Register bit assignment

D00

R/W

RM

0x0

Reverse mode (RevMode)

0

Direct CPU access

1

DMA control

Bits

Access

Mnemonic

Reset

Description

Table 391: IEEE 1284 General Configuration register

Bits

Access

Mnemonic

Reset

Description

D31:27

R

Reserved

0x0

N/A

D26

R/W

RFRIM

0x0

Reverse FIFO ready interrupt mask

(RvFifoRdyInterruptMask)

0

Mask the interrupt

1

Enable the interrupt

D25:24

N/A

Reserved

N/A

N/A

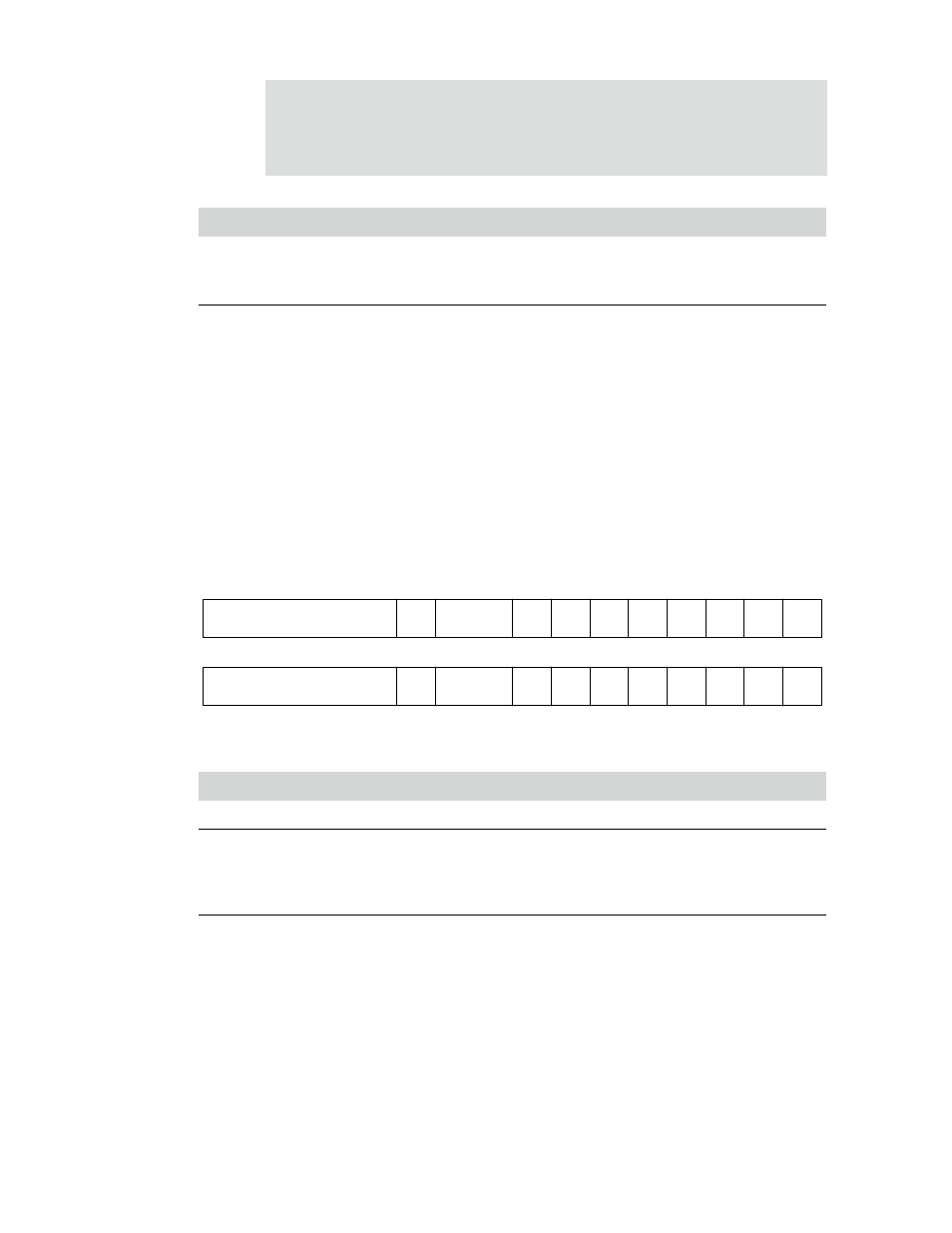

Table 392: Interrupt Status and Control register

RFRI

FDFBG FCFBG FDFMB FCFMB FDFRI FCFRI

PC1I

Rsvd

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

RFRIM

FDBGM FCBGM FDMBM FCMBM FDRIM FCRIM

I1M

Rsvd

Reserved

Reserved

Reserved

Reserved