Digi NS9750 User Manual

Page 437

w w w . d i g i e m b e d d e d . c o m

4 1 3

P C I - t o - A H B B r i d g e

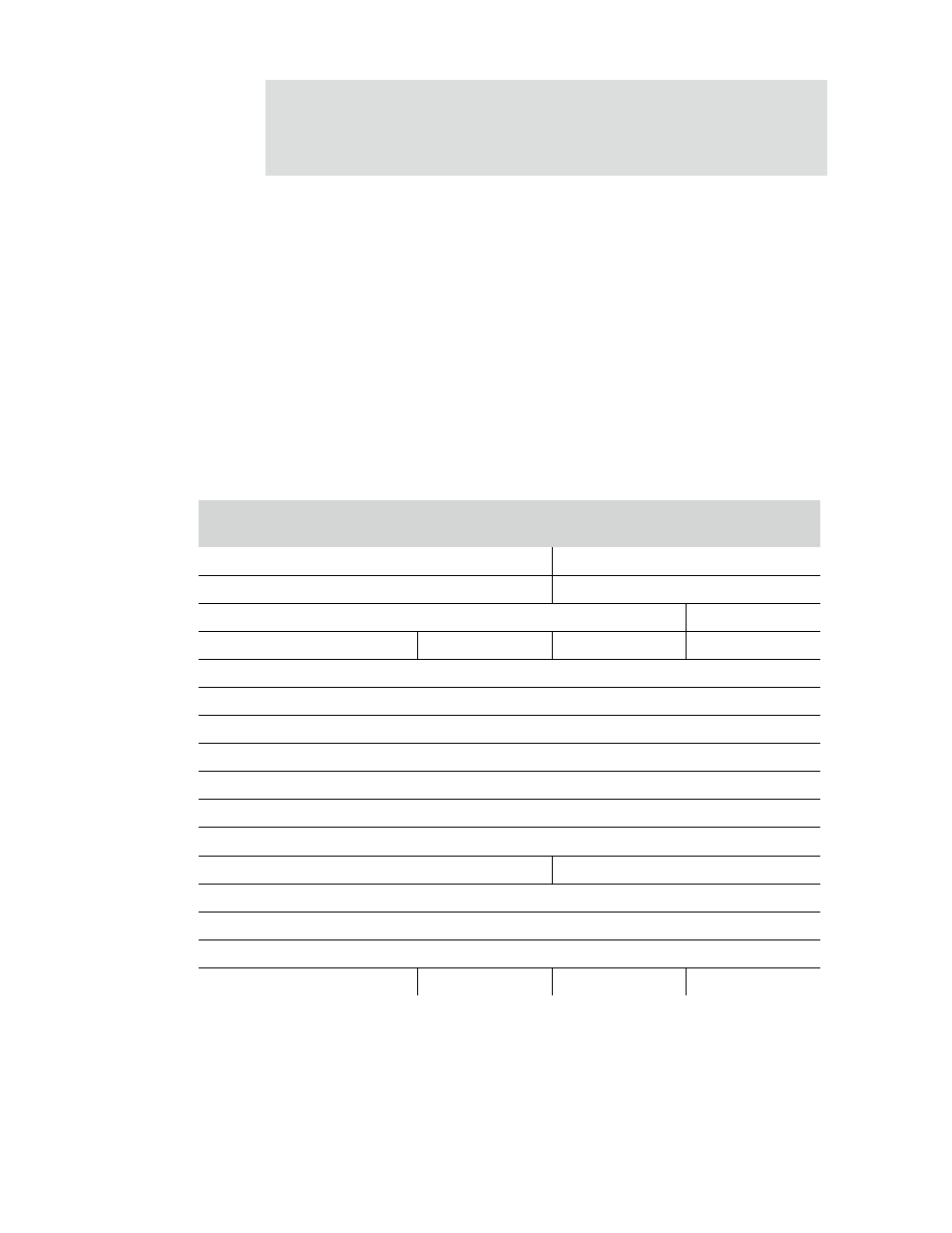

Bridge Configuration registers

Table 254 shows the standard PCI configuration registers that are supported by the

PCI-to-AHB bridge. These registers can be 8-, 16-, or 32-bits wide, as indicated in the

table. The size of the transfer on the AHB bus determines which bytes are written.

All configuration registers must be accessed as 32-bit words and as single accesses

only. Bursting is not allowed.

The registers are described briefly in this chapter. For more information about each

register, see your PCI documentation.

Note:

The register number refers to the

REGISTER_NUMBER

field in the

Configuration Address Port register (see Table 253, “CONFIG_ADDR

register,” on page 411).

Register

number

[31:24]

[23:16]

[15:08]

[07:00]

0x00

Device ID

1

Vendor ID

1

0x01

Status

Command

0x02

Class code

1

Revision ID

1

0x03

BIST

Header

Latency timer

Cache size

0x04

Base address 0

0x05

Base address 1

0x06

Base address 2

0x07

Base address 3

0x08

Base address 4

0x09

Base address 5

0x0A

CardBus CIS pointer

0x0B

Subsystem ID

1

Subsystem vendor ID

1

0x0C

Expansion ROM

0x0D

Reserved

0x0E

Reserved

0x0F

Max_Lat

1

Min_Gnt

1

Interrupt pin

1

Interrupt Line

Table 254: PCI/bridge configuration registers