Bbus bridge interrupt enable register, Enable = set to 1 – Digi NS9750 User Manual

Page 523

w w w . d i g i e m b e d d e d . c o m

4 9 9

B B u s B r i d g e

BBus Bridge Interrupt Enable register

Address: A040 1004

The BBus Bridge Interrupt Enable register allows you to enable or disable BBus

interrupts on an individual basis as well as a global basis. Writing a 1 to a bit enables

the interrupt, allowing it to be included in the aggregate signal that is sent to the

vector interrupt controller in the System Control module. These fields affect only the

generation of the signal sent to the vector interrupt controller (VIC); they do not

affect the originating modules.

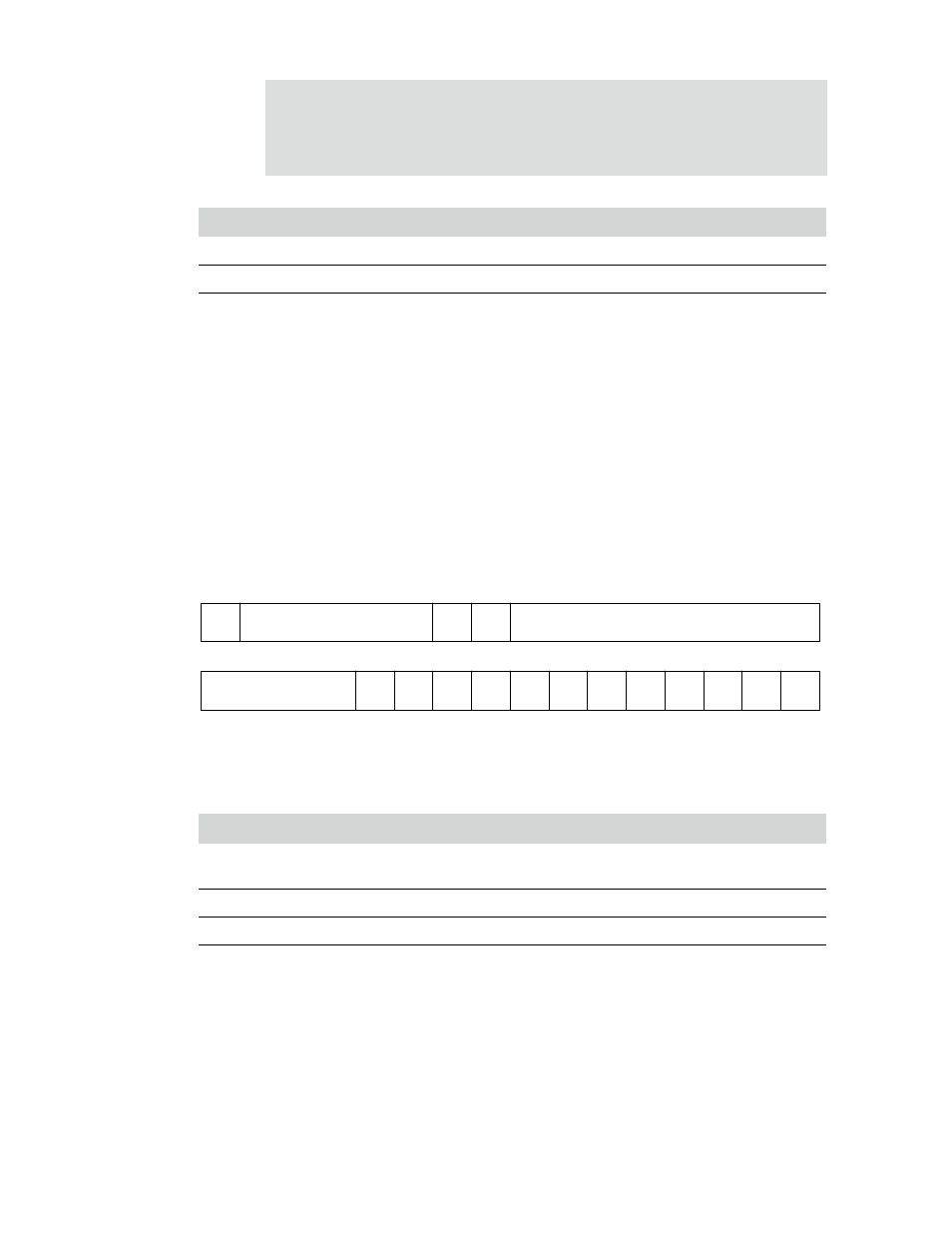

Register bit assignment

Note:

Enable = Set to 1.

D01

R

USB

0

USB module has asserted its interrupt.

D00

R

BBDMA

0

BBus DMA module has asserted its interrupt.

Bits

Access

Mnemonic

Reset

Description

Table 300: BBus Bridge Interrupt Status register

Bits

Access

Mnemonic

Reset

Description

D31

R/W

GLBL

0

Enable the aggregate interrupt signal to propagate to the

VIC in the System Control module.

D30:26

R/W

Not used

0

Always set this field to 0.

D25

R/W

DMA2

0

Enable interrupt from AHB DMA Channel #2.

D24

R/W

DMA1

0

Enable interrupt from AHB DMA Channel #1.

Table 301: BBus Bridge Interrupt Enable register bit definition

Not used

I2CE

1284E

S4TXE S4RXE S3TXE S3RXE S2TXE S2RXE S1TXE S1RXE USBE

DMAE

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

DMA2

DMA1

Not used

Not used

GLBL