Digi NS9750 User Manual

Page 177

w w w . d i g i e m b e d d e d . c o m

1 5 3

M e m o r y C o n t r o l l e r

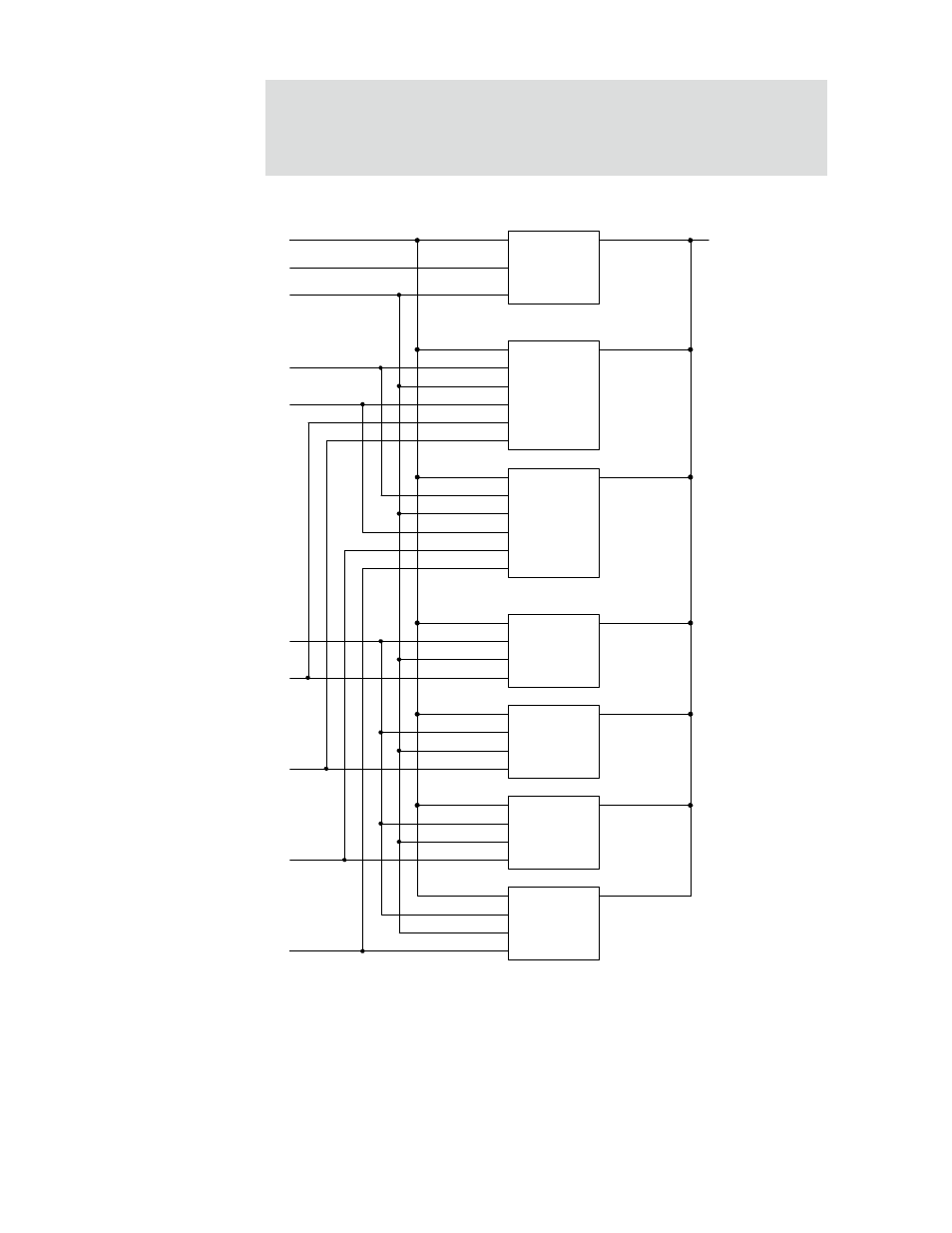

Figure 59: Typical memory connection diagram (1)

DATAOUT[31:0]

DATA

OUT[31:0]

DATAOUT[31:16]

DATAOUT[15:0]

DATAOUT[31:24]

DATAOUT[23:16]

DATAOUT[15:8]

DATAOUT[7:0]

Q[31:0]

2Mx32 burst mask ROM

64Kx16 SRAM, two off

128Kx8 SRAM, four off

A[15:0]

CE_n

OE_n

WE_n

UB_n

LB_n

IO[15:0]

A[15:0]

CE_n

OE_n

WE_n

UB_n

LB_n

IO[15:0]

A[16:0]

CE_n

OE_n

WE_n

IO[7:0]

A[16:0]

CE_n

OE_n

WE_n

IO[7:0]

A[16:0]

CE_n

OE_n

WE_n

IO[7:0]

A[16:0]

CE_n

OE_n

WE_n

IO[7:0]

ADDROUT[20:0]

ADDROUT[15:0]

ADDROUT[15:0]

ADDROUT[16:0]

ADDROUT[16:0]

ADDROUT[16:0]

ADDROUT[16:0]

A[20:0]

CE_n

OE_n

ADDROUT[20:0]

STCSOUT[0]_n

OEOUT_n

STCSOUT[1]_n

WEOUT_n

STCSOUT[2]_n

BLSOUT[3]_n

BLSOUT[2]_n

BLSOUT[1]_n

BLSOUT[0]_n