Digi NS9750 User Manual

Page 227

w w w . d i g i e m b e d d e d . c o m

2 0 3

M e m o r y C o n t r o l l e r

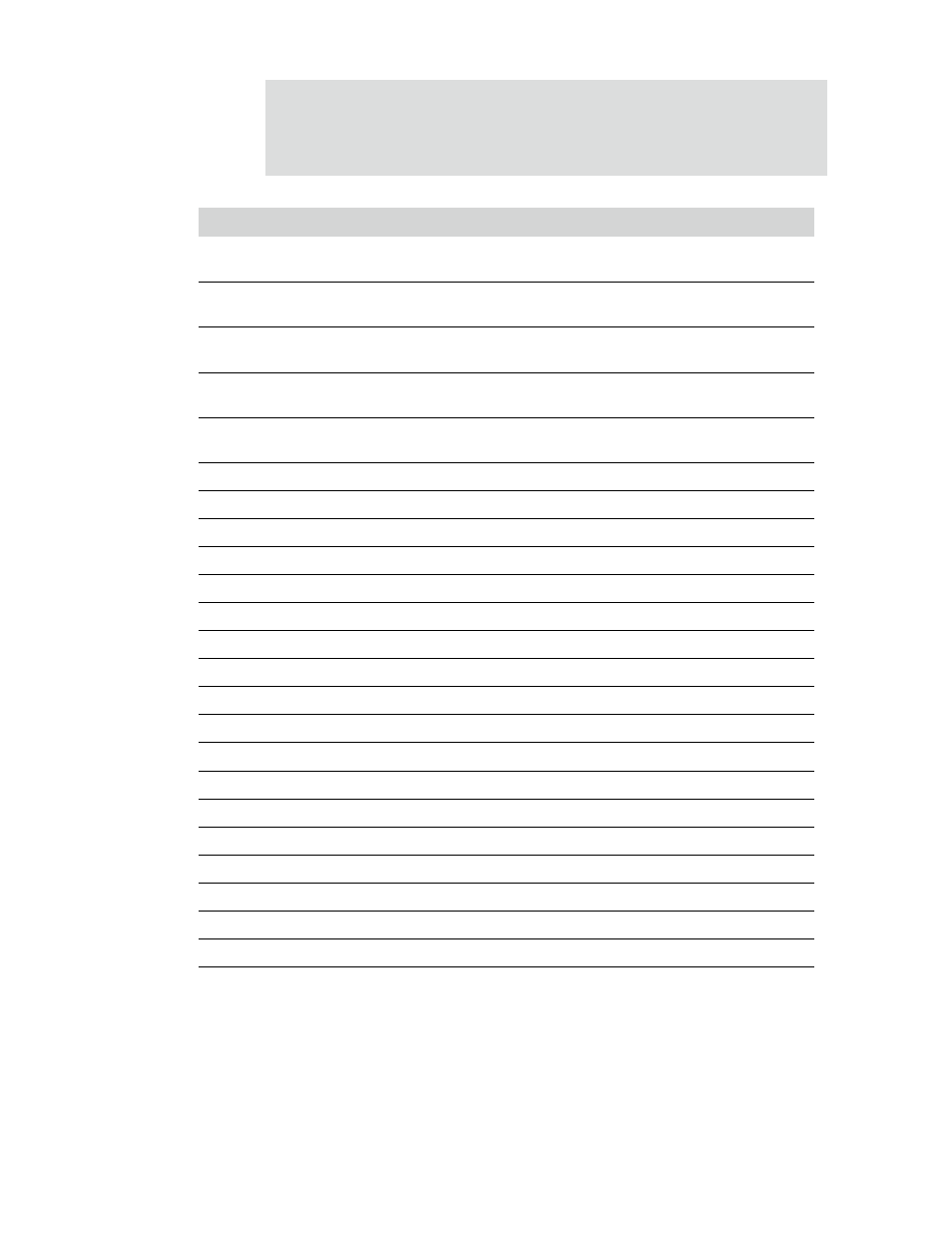

A070 0048

DynamictRC

Dynamic Memory Active to Active Command Period

(t

RC

)

A070 004C

DynamictRFC

Dynamic Memory Auto Refresh Period, and Auto

Refresh to Active Command Period (t

RFC

)

A070 0050

DynamictXSR

Dynamic Memory Exit Self-Refresh to Active

Command (t

XSR

)

A070 0054

DynamictRRD

Dynamic Memory Active Bank A to Active B Time

(t

RRD

)

A070 0058

DynamictMRD

Dynamic Memory Load Mode register to Active

Command Time (t

MRD

)

A070 0080

StaticExtendedWait

Static Memory Extended Wait

A070 0100

DynamicConfig0

Dynamic Memory Configuration Register 0

A070 0104

DynamicRasCas0

Dynamic Memory RAS and CAS Delay 0

A070 0120

DynamicConfig1

Dynamic Memory Configuration Register 1

A070 0124

DynamicRasCas1

Dynamic Memory RAS and CAS Delay 1

A070 0140

DynamicConfig2

Dynamic Memory Configuration Register 2

A070 0144

DynamicRasCas2

Dynamic Memory RAS and CAS Delay 2

A070 0160

DynamicConfig3

Dynamic Memory Configuration Register 3

A070 0164

DynamicRasCas3

Dynamic Memory RAS and CAS Delay 3

A070 0200

StaticConfig0

Static Memory Configuration Register 0

A070 0204

StaticWaitWen0

Static Memory Write Enable Delay 0

A070 0208

StaticWaitOen0

Static Memory Output Enable Delay 0

A070 020C

StaticWaitRd0

Static Memory Read Delay 0

A070 0210

StaticWaitPage0

Static Memory Page Mode Read Delay 0

A070 0214

StaticWaitWr0

Static Memory Write Delay 0

A070 0218

StaticWaitTurn0

Static Memory Turn Round Delay 0

A070 0220

StaticConfig1

Static Memory Configuration Register 1

A070 0224

StaticWaitWen1

Static Memory Write Enable Delay 1

A070 0228

StaticWaitOen1

Static Memory Output Enable Delay 1

Address

Register

Description

Table 137: Memory Controller register map