Digi NS9750 User Manual

Page 819

w w w . d i g i e m b e d d e d . c o m

7 9 5

T i m i n g

Memory timing

Note:

All AC characteristics are measured with 35pF, unless otherwise noted.

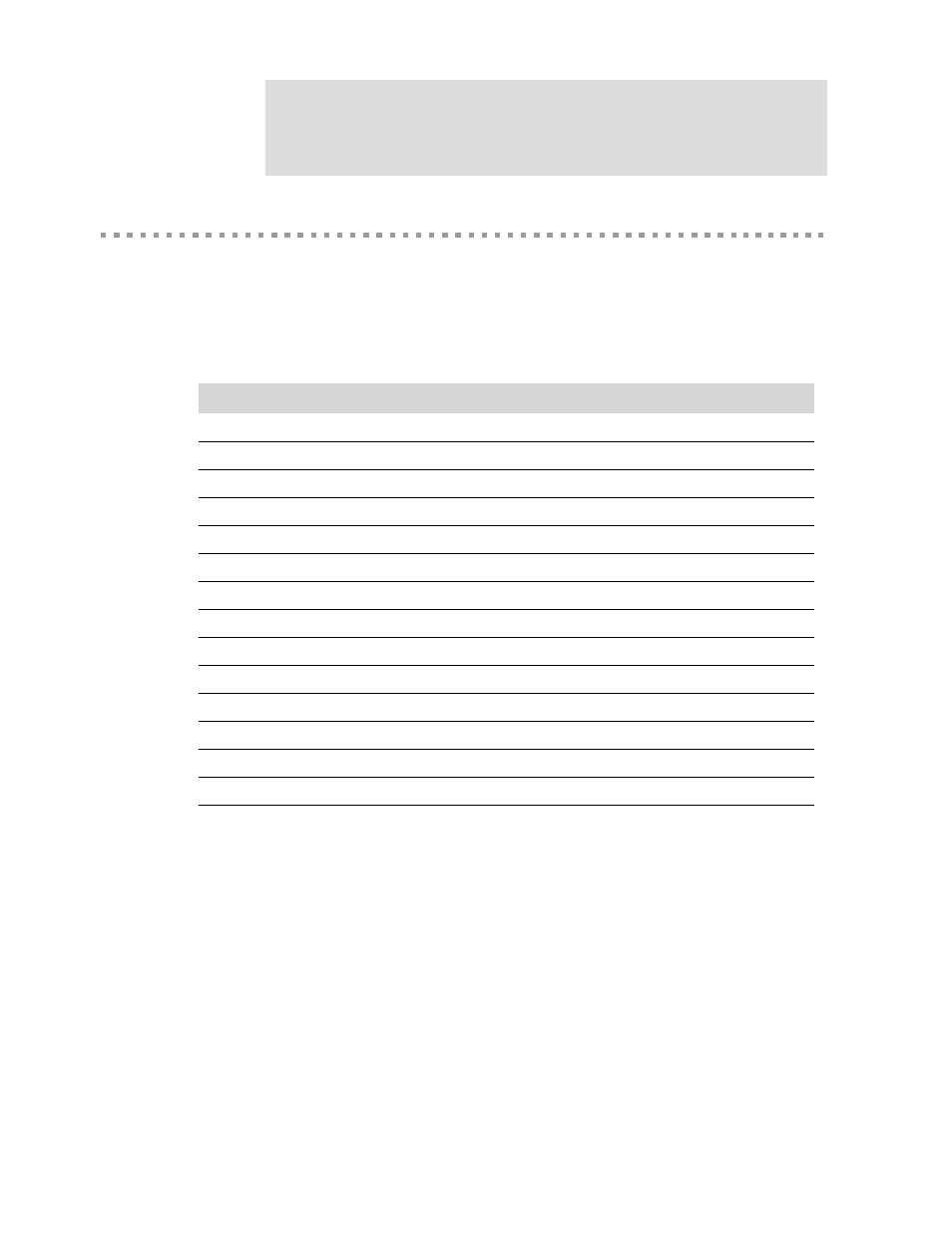

Memory timing contains parameters and diagrams for both SDRAM and SRAM timing.

Table 467 describes the values shown in the SDRAM timing diagrams (Figure 104

through Figure 112).

Notes:

1

All four data_mask signals are used for all transfers.

2

All four data_mask signals will go low during a read cycle, for both 16-bit and 32-bit transfers.

3

Only one of the four

clk_out

signals is used.

4

Only one of the four

dy_cs_n

signals is used.

Parm

Description

Min

Max

Unit

Notes

M1

data input setup time to rising

1.6

ns

M2

data input hold time to rising

3.3

ns

M3

clk_out high to clk_en high

6.1

ns

M4

clk_out high to address valid

6.1

ns

M5

clk_out high to data_mask

6.1

ns

1, 2

M6

clk_out high to dy_cs_n low

6.1

ns

3, 4

M7

clk_out high to ras_n low

6.1

ns

M8

clk_out high to cas_n low

6.1

ns

M9

clk_out high to we_n low

6.1

ns

M10

clk_out high to data out

6.2

ns

M11

address hold time

3.5

M12

data out hold time

3.8

M13

clk_en high to sdram access

2

2

clock

M14

end sdram access to clk_en low

2

2

clock

Table 467: SDRAM timing parameters