Digi NS9750 User Manual

Page 145

w w w . d i g i e m b e d d e d . c o m

1 2 1

M e m o r y C o n t r o l l e r

Static memory controller

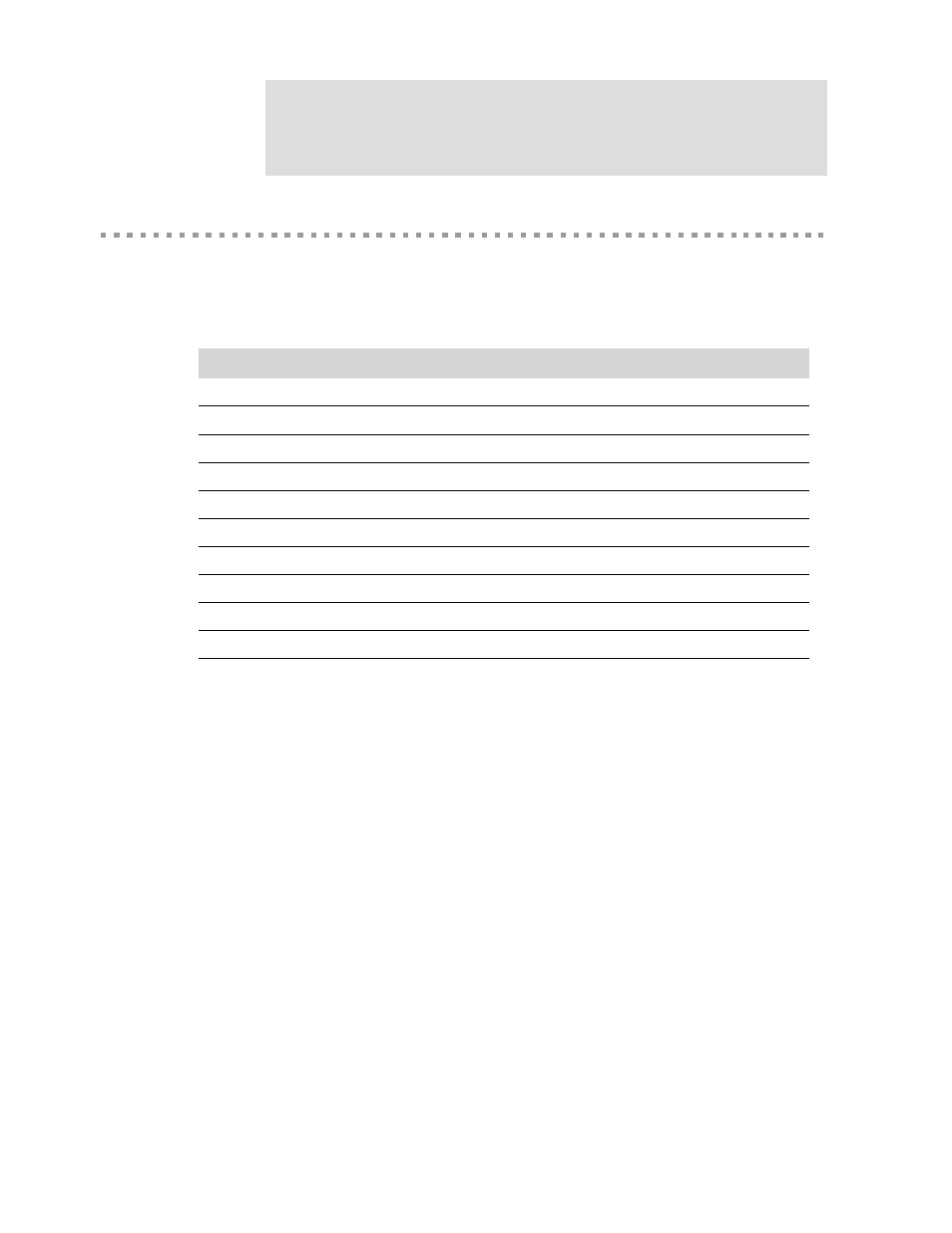

Table 48 shows configurations for the static memory controller with different types of

memory devices. See "Static Memory Configuration 0–3 registers" on page 230 for

more information.

Notes:

Buffering enables the transaction order to be rearranged to improve

memory performance. If the transaction order is important, the buffers

must be disabled.

Extended wait and page mode cannot be enabled at the same time.

Device

Write protect

Page mode

Buffer

ROM

Enabled

Disabled

Disabled

a

Page mode ROM

Enabled

Enabled

Enabled

a

Extended wait ROM

Enabled

Disabled

Disabled

a

SRAM

Disabled (or enabled)

b

Disabled

Disabled

a

Page mode SRAM

Disabled (or enabled)

b

Enabled

Enabled

a

Extended wait SRAM

Disabled (or enabled)

b

Disabled

Disabled

a

Flash

Disabled or (enabled)

b

Disabled

Disabled

c

Page mode flash

Disabled or (enabled)

b

Enabled

Enabled

c

Extended wait flash

Disabled or (enabled)

b

Disabled

Disabled

a

Memory mapped peripheral

Disabled (or enabled)

b

Disabled

Disabled

a

Enabling the buffers means that any access causes the buffer to be used. Depending on the

application, this can provide performance improvements. Devices without async-page-mode

support generally work better with the buffer disabled. Again, depending on the application, this

can provide performance improvements.

b

SRAM and Flash memory devices can be write-protected if required.

c

Buffering must be disabled when performing Flash memory commands and during writes.

Table 48: Static memory controller configurations