Register bit assignment – Digi NS9750 User Manual

Page 806

U S B D e v i c e E n d p o i n t F I F O C o n t r o l a n d D a t a r e g i s t e r s

7 8 2

N S 9 7 5 0 H a r d w a r e R e f e r e n c e

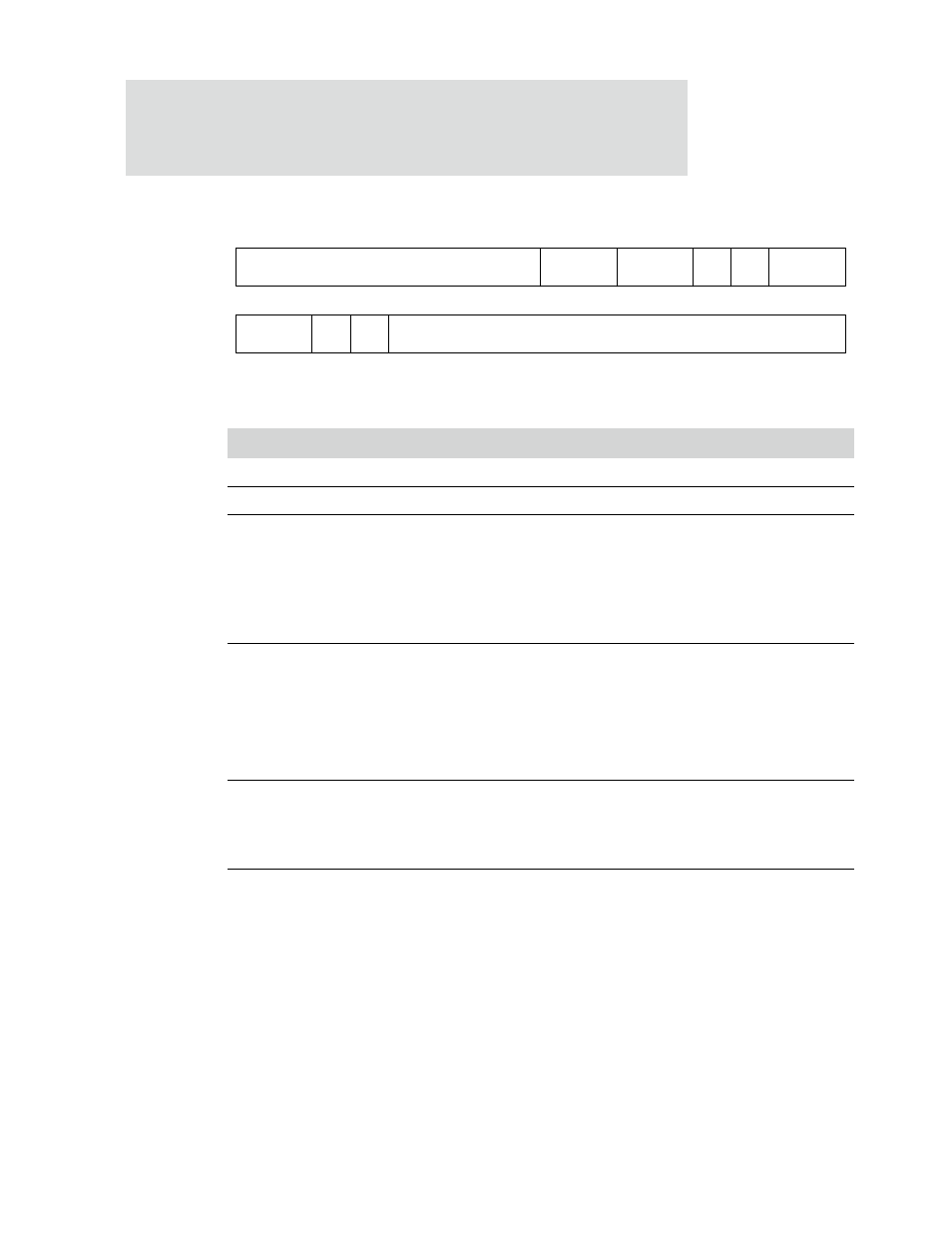

Register bit assignment

Bits

Access

Mnemonic

Reset

Description

D31:24

N/A

Reserved

N/A

N/A

D23:22

R/W

Not used

0x0

Always write as 00.

D21:20

R/W

TYPE

0x0

Type field

Defines the endpoint type associated with the FIFO.

00

Control

01

Isochronous

10

Bulk

11

Interrupt

D19

R/W

CLR

1

Clear field

Writing a 1 places the FIFO into the reset state, disabling

the associated endpoint. Any data currently in the FIFO is

flushed.

When the endpoint is configured for the IN direction and

the type is either bulk or interrupt, this bit is also set to 1

by the hardware when a packet error is found by the host.

D18

R/W

DIR

0

Direction field

0

Defines the OUT direction

1

Defines the IN direction

Defines the FIFO (endpoint) direction.

D17:16

R

FDB

0x0

Valid data bytes

Indicates the valid number of bytes in the FIFO when

receiving; this field is always 0 when transmitting.

Note:

This field is not used when using the DMA

controller.

Table 459: FIFO Status and Control registers

M31

M30

CIA

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

STATE

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Reserved

TYPE

CLR

DIR

FDB

Not used