Digi NS9750 User Manual

Page 520

B B u s B r i d g e C o n t r o l a n d S t a t u s r e g i s t e r s

4 9 6

N S 9 7 5 0 H a r d w a r e R e f e r e n c e

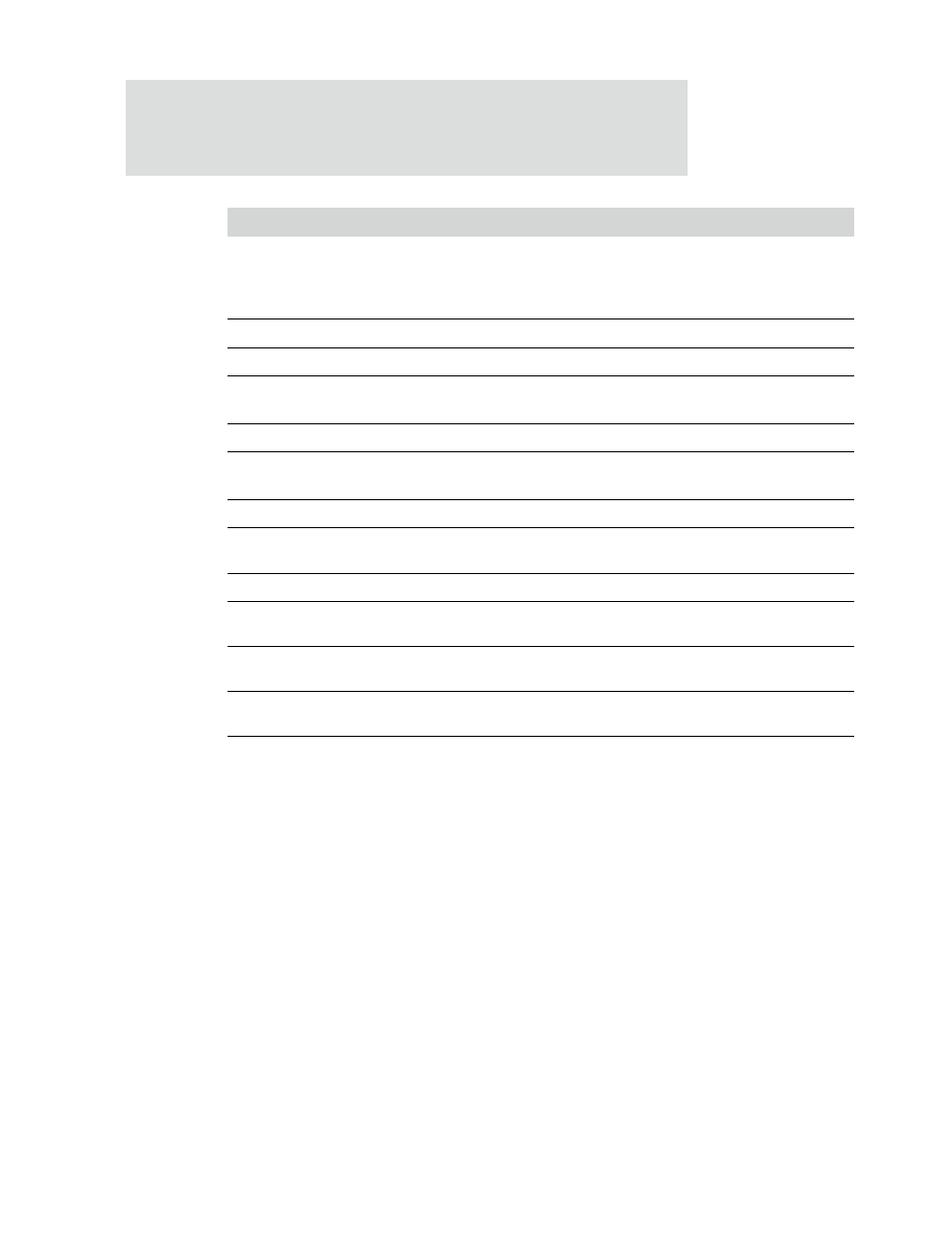

DMA Peripheral Chip Select register

Address: A040 000C / 002C

The DMA Peripheral Chip Select register contains the DMA peripheral chip select

definition. The BBus bridge contains a DMA Peripheral Chip Select register for each

channel.

D27

RW1TC

PCIP

0

Premature complete interrupt pending

Set when a DMA transfer is terminated by assertion of

the

dma_done

signal. NCIP is set when PCIP is set, for

backward compatibility.

D26:25

R/W

Not used

0

Always set this field to 0.

D24

R/W

NCIE

0x0

Enable NCIP interrupt generation

D23

R/W

ECIE

0x0

Enable ECIP interrupt generation

Always enable during normal operation.

D22

R/W

NRIE

0x0

Enable NRIP interrupt generation

D21

R/W

CAIE

0x0

Enable CAIP interrupt generation

Always enable during normal operation.

D20

R/W

PCIE

0x0

Enable PCIP interrupt generation

D19

R

WRAP

0x0

Debug field, indicating the last descriptor in the buffer

descriptor list.

D18

R

IDONE

0x0

Debug field, indicating an interrupt on done occurrence.

D17

R

LAST

0x0

Debug field, indicating the last buffer descriptor in the

current data frame.

D16

R

FULL

0x0

Debug field, indicating the status of the F bit from the

current DMA buffer descriptor.

D15:00

R

BLEN

0x0000

Debug field, indicating the remaining byte transfer

count.

Bits

Access

Mnemonic

Reset

Description

Table 298: DMA Status and Interrupt Enable register bit definition