Serial channel b/a/c/d bit-rate register – Digi NS9750 User Manual

Page 684

S e r i a l p o r t c o n t r o l a n d s t a t u s r e g i s t e r s

6 6 0

N S 9 7 5 0 H a r d w a r e R e f e r e n c e

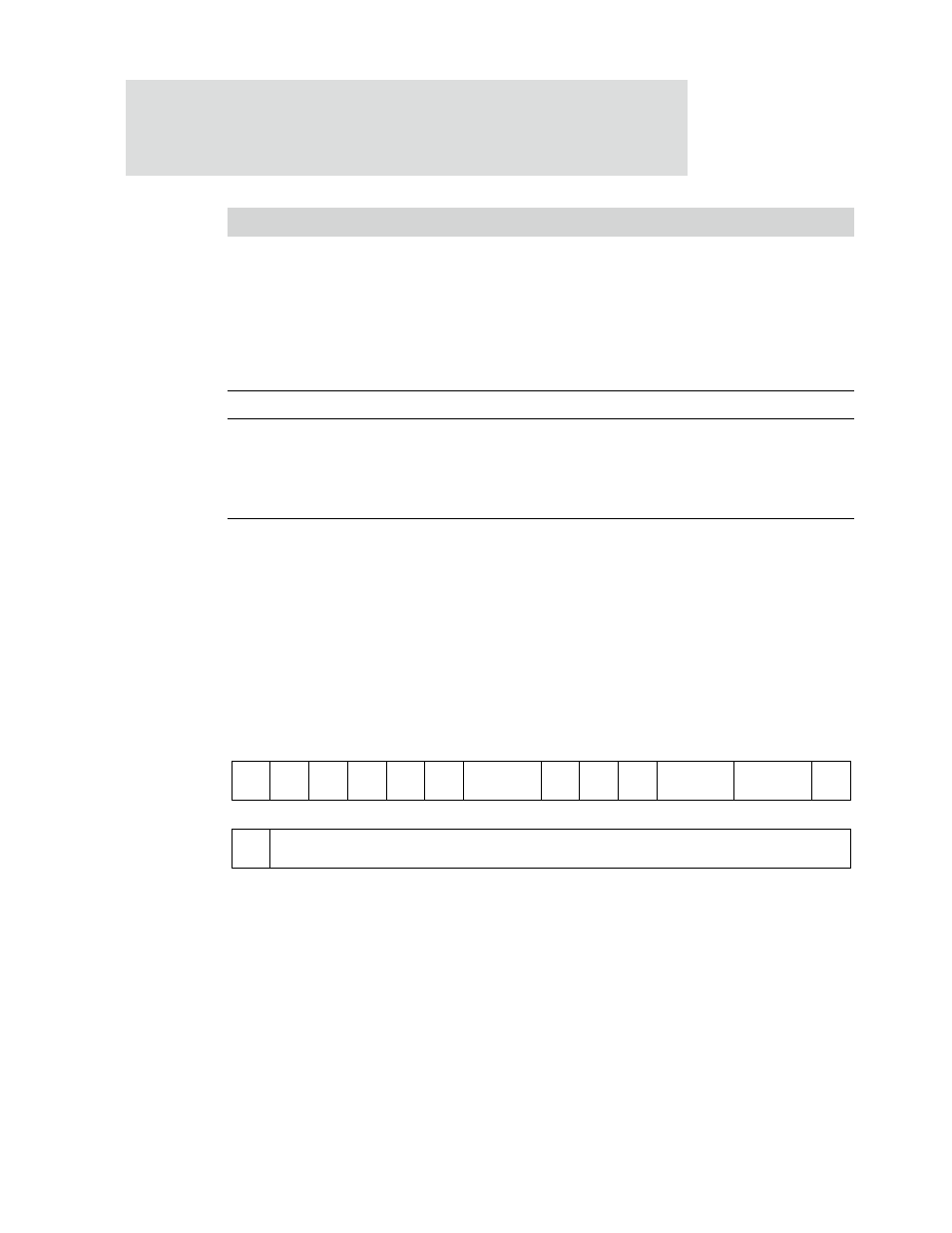

Serial Channel B/A/C/D Bit-rate register

Address: 9020 000C / 004C

9030 000C / 004C

The Serial Channel B/A/C/D Bit-rate register contains the serial channel timing

reference control bits and the data rate control bits.

D02

R

THALF

0

Transmit FIFO half empty

Indicates that the transmit data FIFO contains room for at

least 16 bytes. THALF typically is used only in interrupt-

driven applications; this field is not used for DMA

operation.

The THALF status condition can be programmed to

generate an interrupt by setting the corresponding IE bit in

Serial Channel Control Register A.

D01

N/A

Reserved

N/A

N/A

D00

R

TEMPTY

0

Transmit FIFO empty

Indicates that the transmit data FIFO currently is empty.

TEMPTY simply reports the status of the FIFO; this bit

does not indicate that the character currently in the

Transmit Shift register has been transmitted.

Bits

Access

Mnemonic

Reset

Description

Table 386: Serial Channel B/A/C/D Status Register A

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

RICS

N (divisor value)

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

RXSRC

TX

SRC

TX

EXT

RX

EXT

CLKMUX

TXC

INV

RXC

INV

SPC

POL

TDCR

TICS

EBIT

T

MODE

RDCR