Register bit assignment, Table 209: ethernet transmit status register – Digi NS9750 User Manual

Page 369

w w w . d i g i e m b e d d e d . c o m

3 4 5

E t h e r n e t C o m m u n i c a t i o n M o d u l e

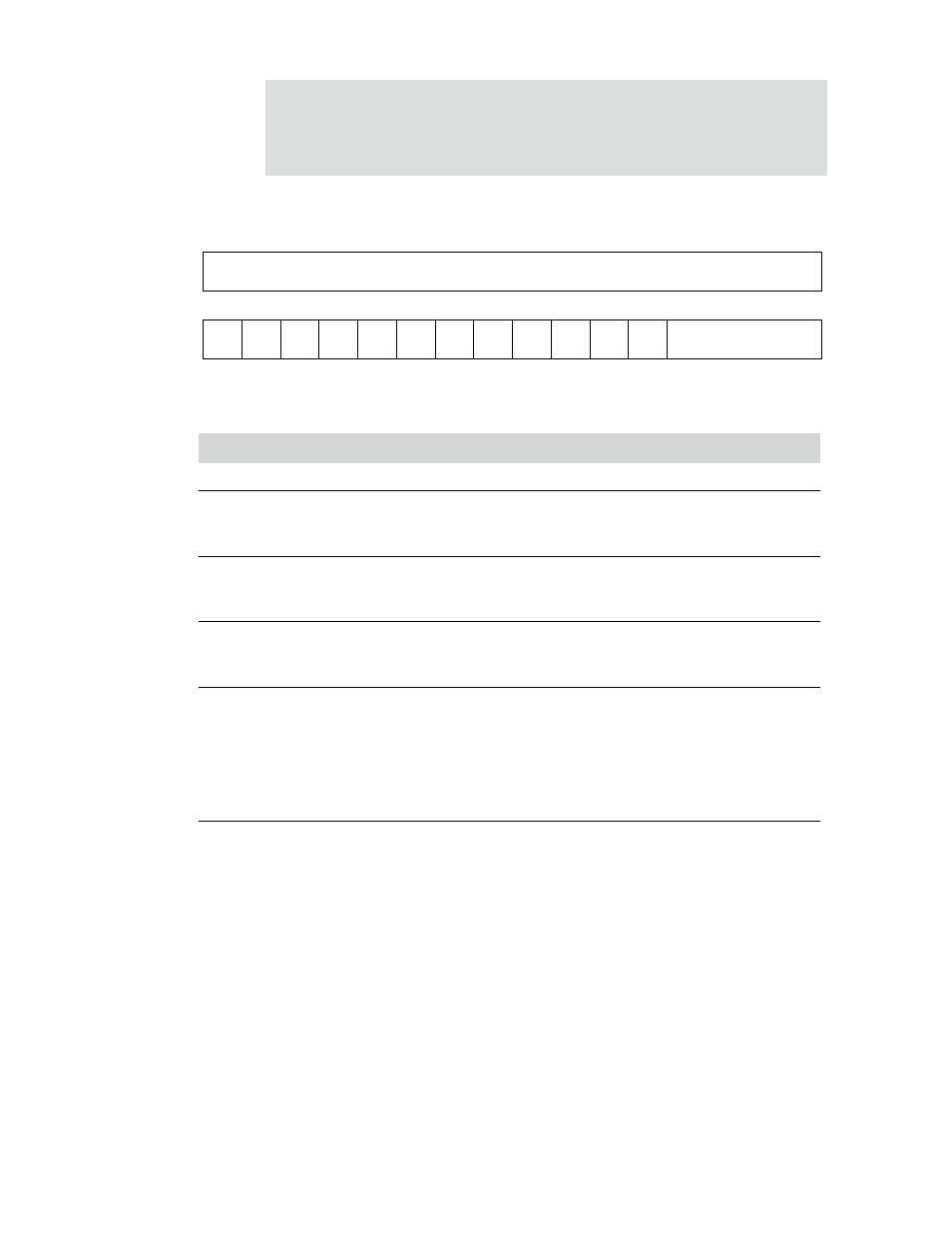

Register bit assignment

Bits

Access

Mnemonic

Reset

Description

D31:16

N/A

Reserved

N/A

N/A

D15

R

TXOK

0x0

Frame transmitted OK

When set, indicates that the frame has been delivered to

and emptied from the transmit FIFO without problems.

D14

R

TXBR

0x0

Broadcast frame transmitted

When set, indicates the frame’s destination address was

a broadcast address.

D13

R

TXMC

0x0

Multicast frame transmitted

When set, indicates the frame’s destination address was

a multicast address.

D12

R

TXAL

0x0

TX abort — late collision

When set, indicates that the frame was aborted due to a

collision that occurred beyond the collision window set

in the Collision Window/Retry register (see page 366).

If this bit is set, the

TX_WR

logic stops processing

frames and sets the TXERR bit in the Ethernet Interrupt

Status register.

D11

R

TXAED

0x0

TX abort — excessive deferral

When set, indicates that the frame was deferred in

excess of 6071 nibble times in 100 Mbps or 24,287

times in 0 Mbps mode. This causes the frame to be

aborted if the excessive deferral bit is set to 0 in MAC

Configuration Register #2 (see page 351). If TXAED is

set, the

TX_WR

logic stops processing frames and sets

the TXERR bit in the Ethernet Interrupt Status register.

Table 209: Ethernet Transmit Status register

Reserved

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Not

used

TX

DEF

TX

CRC

Not

used

TXCOLC

TX

OK

TX

BR

TX

MC

TX

AL

TX

AED

TX

AEC

TX

AUR

TX

AJ