Ethernet general control register #1, Register bit assignment, Table 206: ethernet general control register #1 – Digi NS9750 User Manual

Page 363

w w w . d i g i e m b e d d e d . c o m

3 3 9

E t h e r n e t C o m m u n i c a t i o n M o d u l e

Ethernet General Control Register #1

Address: A060 0000

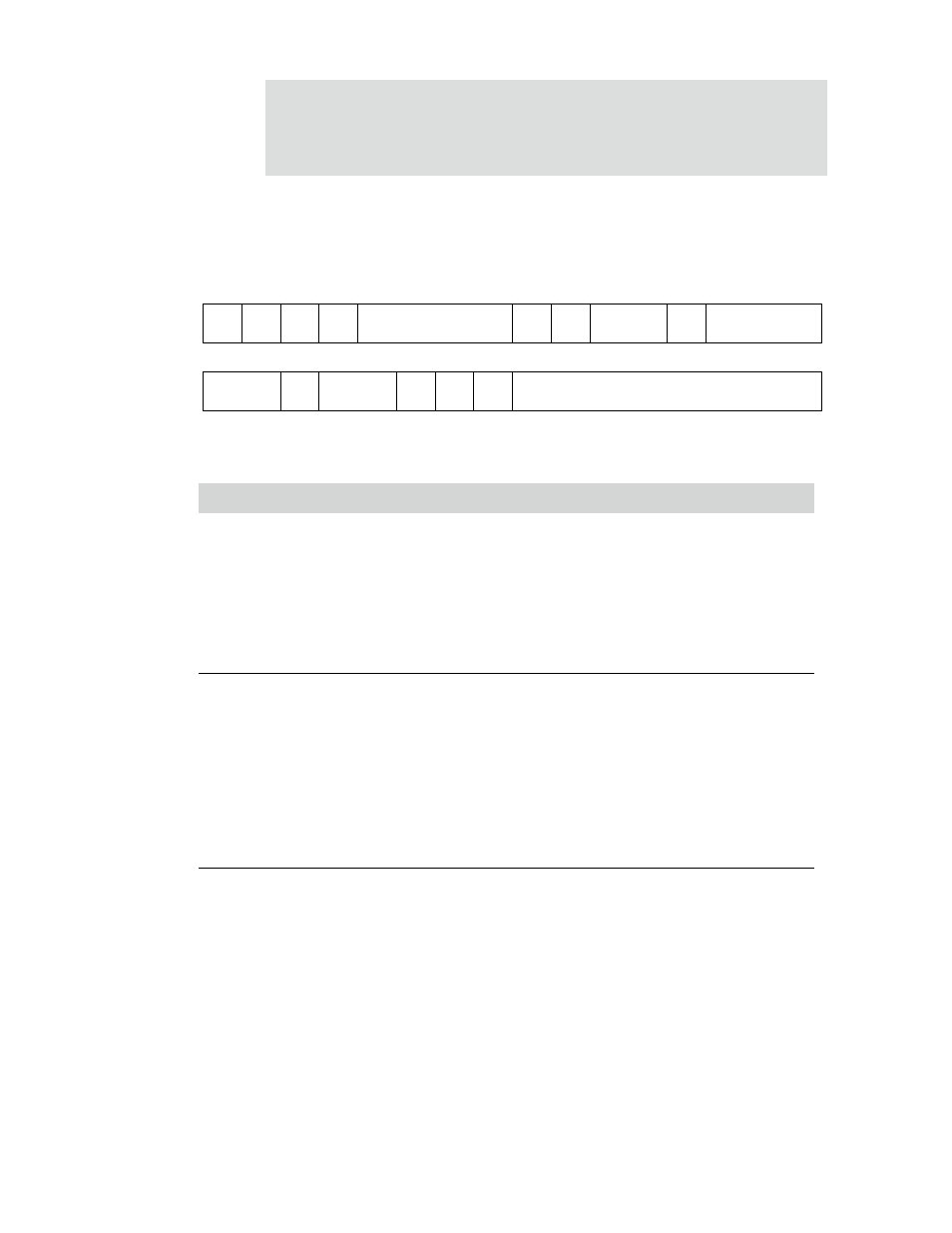

Register bit assignment

Bits

Access

Mnemonic

Reset

Description

D31

R/W

ERX

0

Enable RX packet processing (see "Receive packet

processor" on page 324)

0

Reset RX

1

Enable RX

Used as a soft reset for the RX. When cleared, resets all

logic in the RX and flushes the FIFO.

The ERX bit must be set active high to allow data to be

received from the MAC receiver.

D30

R/W

ERXDMA

0

Enable receive DMA

0

Disable receive DMA data request (use to stall

receiver)

1

Enable receive DMA data request

Must be set active high to allow the

RX_RD

logic to

request the AHB bus to DMA receive frames into system

memory.

Set this bit to zero to temporarily stall the receive side

Ethernet DMA. The

RX_RD

logic stalls on frame

boundaries.

D29

N/A

Reserved

N/A

N/A

Table 206: Ethernet General Control Register #1

RX

ALIGN

MAC_

HRST

ITXA

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

PHY_MODE

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

Rsvd

ERX

SHT

Not used

ETX

ETX

DMA

Not

used

ERX

INIT

ERX

ERX

DMA

Reserved

Reserved

Not used

Rsvd