Digi NS9750 User Manual

Page 321

w w w . d i g i e m b e d d e d . c o m

2 9 7

S y s t e m C o n t r o l M o d u l e

The Miscellaneous System Configuration and Status register configures miscellaneous

system configuration bits.

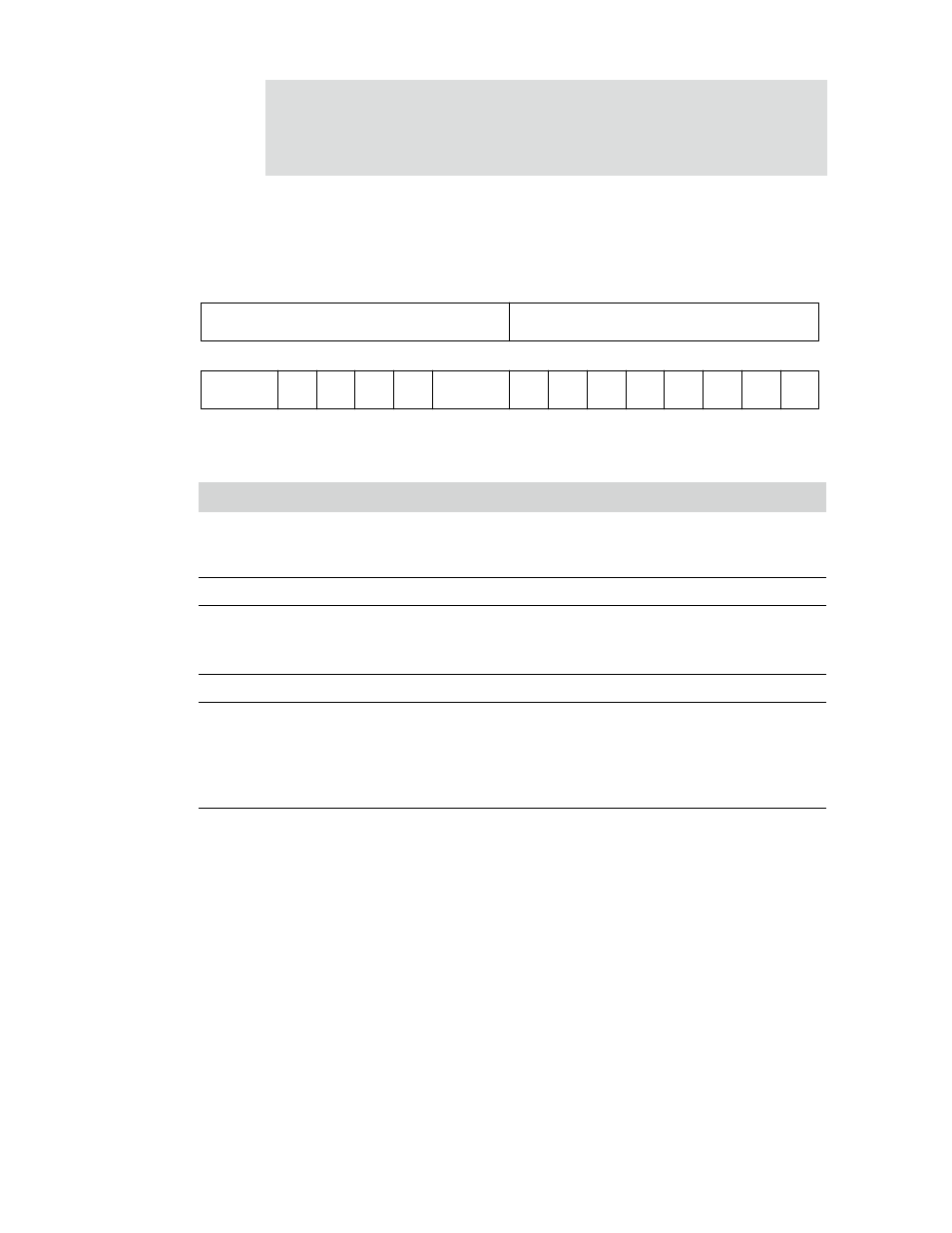

Register bit assignment

Bits

Access

Mnemonic

Reset

Description

D31:24

R

REV

0x0

Revision

Indicates the NS9750 hardware identification and

revision.

D23:14

N/A

Reserved

N/A

N/A

D13

R

PCIA

0x1

PCI arbiter configuration

0

External PCI arbiter

1

Internal PCI arbiter

D12

N/A

Reserved

N/A

N/A

D11

R

BMM

HW strap

reset_done

Bootup memory mode

0

Boot from SDRAM using SPI serial EEPROM

1

Boot from Flash/ROM on memory chip

select 1

Status only; indicates the bootup process.

D10

R

CS1DB

HW strap

boot_strap[

0]

Chip select 1 data byte lane configuration HW strap

setting

Status bit indicating the hardware strap setting of

external memory chip select 1 byte lane/write enable

signal configuration. This configuration can be changed

by writing to the appropriate control register in the

memory controller.

Table 187: Miscellaneous System Configuration and Status register

PCIA

Rsvd

CS1DB

BMM

CS1DW

MCCM PMSS

CS1P

Rsvd

ENDM MBAR Rsvd

IRAM0

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

14

31

29

28

27

26

25

24

23

22

21

20

19

18

17

16

30

REV

Reserved

Reserved