Digi NS9750 User Manual

Page 51

w w w . d i g i e m b e d d e d . c o m

2 7

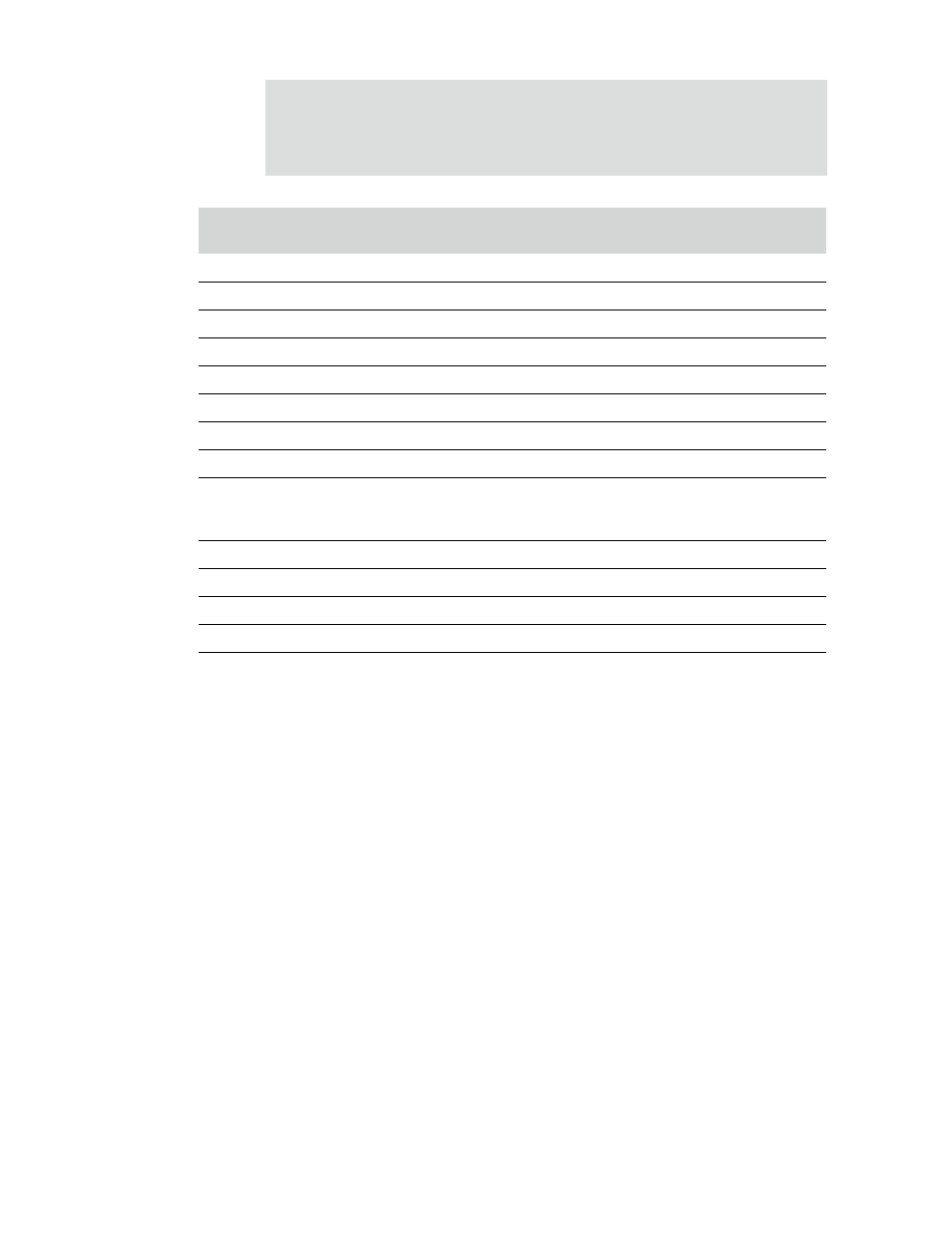

N S 9 7 5 0 P i n o u t

AD20

bist_en_n

I

Enable internal BIST operation

AF21

pll_test_n

I

Enable PLL testing

AE21

scan_en_n

I

Enable internal scan testing

B18

sys_pll_dvdd

System clock PLL 1.5V digital power

A18

sys_pll_dvss

System clock PLL digital ground

B17

sys_pll_avdd

System clock PLL 3.3V analog power

C17

sys_pll_avss

System clock PLL analog ground

J2

lcdclk

U

I

External LCD clock input

T2

boot_strap[0]

U

2

I/O

Chip select 1 static memory byte_lane_enable_n,

or write_enable_n for byte-wide devices

bootstrap select

N3

boot_strap[1]

U

2

I/O

CardBus mode bootstrap select

P1

boot_strap[2]

U

2

I/O

Memory interface read mode bootstrap select

P2

boot_strap[3]

U

2

I/O

Chip select 1 data width bootstrap select

P3

boot_strap[4]

U

2

I/O

Chip select 1 data width bootstrap select

Pin #

Signal name

U/D

OD

(mA)

I/O

Description

Table 6: Clock generation and system pin pinout